Research interrests

FEDER project

The project aims at developing a flexible architecture of channel code decoding for the 5G networks (wireless broadband, IoT, M2M).

Duration: 2017 - 2019

European Flagships project

The Human Brain Project should lay the technical foundations for a new model of ICT-based brain research, driving integration between data and knowledge from different disciplines, and catalysing a community effort to achieve a new understanding of the brain, new treatments for brain disease and new brain-like computing technologies.

Duration: 2012 - 2022

European Network of Excellence on High Performance and Embedded Architecture and Compilation

Funded under 7th FWP (EU Seventh Framework Programme, FP7).

Duration: 2010 - 2014

The SENSE project is a Labex CominLabs' project that gathers academic partners in order to develop the next-generation artificial vision system inspired from biological eyes.

The main goals are the following:

The GRAAL project is a project dedicated construct an idustrial demonstrator for a technology proposed on one of our patents.

The main goals are the following:

The GigaDEC project is a French project that gathers industrial and academic partners in order to develop the next-generation of very high throughput (Giga) signal coder/decoder (DEC).

The main goals are the following:

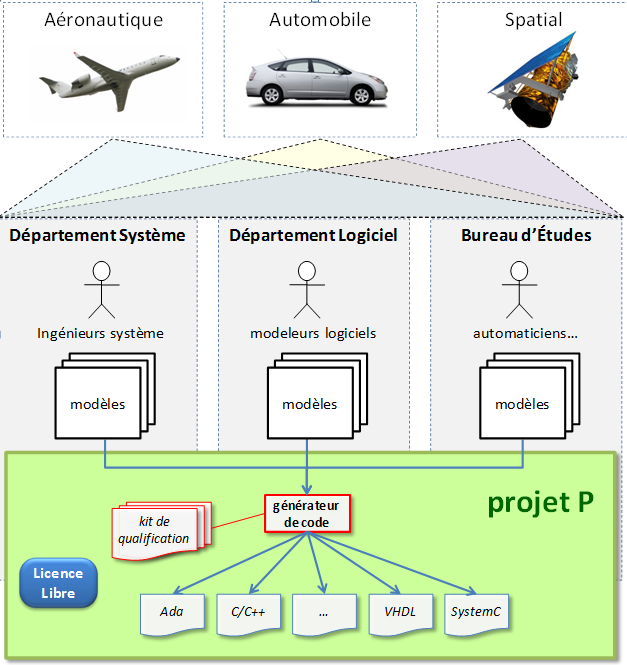

The P project is a French project that gathers industrial and academic partners from the Aerospace Valley and Systematic pôles to address the issue of Model-Driven design methodologies for critical embedded systems.

The main goals are the following:

The SoCKET project (SoC toolKit for critical Embedded sysTems) is a French project that gathers industrial and academic partners from the Aerospace Valley and Minalogic pôles to address the issue of design methodologies for critical embedded systems.

The main goals are the following:

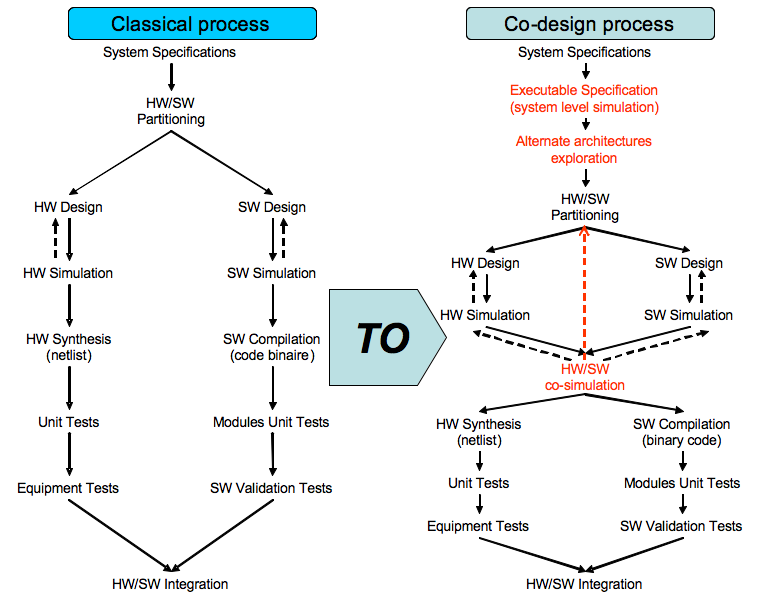

High-level synthesis (HLS), sometimes referred to as C synthesis, electronic system level (ESL) synthesis, algorithmic synthesis, or behavioral synthesis, is an automated design process that interprets an algorithmic description of a desired behavior and creates hardware that implements that behavior [HLS]. The starting point of a high-level synthesis flow is ANSI C/C++/SystemC code. The code is analyzed, architecturally constrained, and scheduled to create a register transfer level hardware design language (HDL), which is then in turn commonly synthesized to the gate level by the use of a logic synthesis tool. The goal of HLS is to let hardware designers efficiently build and verify hardware, by giving them better control over optimization of their design architecture, and through the nature of allowing the designer to describe the design at a higher level of tools while the tool does the RTL implementation. Verification of the RTL is an important part of the process [EE Times].