Biographie

Cyrille Chavet a obtenu un D.E.A. Informatique: Système et Communication (Master 2) et un Magistère Informatique à l'Université Joseph Fourier, 2003, Grenoble, France, et une Thèse de doctorat en Informatique et Sciences de l'ingénieur de l'Université Bretagne Sud, 2004-2007, Lorient, France.

After 3 years of industrial experience in Europe (STMicroelectronics) in Computer-Aided Design, High Level Synthesis, digital circuits and telecommunication systems, he has spent 4 years in academia with the TIMA laboratory (Universitée Joseph fourier, Grenoble, France) and with the Lab-STICC Universitée de Bretagne-Sud at Lorient, France. He is currently an Associate Professor with the Lab-STICC Laboratory, Universitée Bretagne-Sud.

His current research interests include high-level synthesis, memory mapping problems, advanced neural network architectures and post-quantum cryptography. He has published more than 40 papers in edited books, journals or conference proceedings on these topics and holds 4 patents in hardware design domain.

He is co-editor of the book "Advanced Hardware Design for Error Correcting Codes" (Springer). He has organized workshops in international conferences HiPEAC (2012, 2013, 2014), GLS-VLSI (2015). He also serves as session chair in international IEEE conferences (SiPS), as PC member in international ACM/IEEE conferences (DASIP, ARC) or as a reviewer (DATE, ICASSP, ISCAS, ASAP, GLSVLSI, SIPS, DAC, FPL, DASIP...) and as reviewer for journals.

He is also co-author of a chapter of the books, High Level Synthesis: from Algorithm to Digital Circuit (Coussy P. & Morawiec A. (Eds.), Springer, 2008).

Domaine de recherche

Je m'intèresse aux outils et méthodes pour les outils d'aide à la conception de cicuit (Computer Aided Design) en partant d'une spécification exécutable pour générer une architecture synthétisable. Pour développer des outils CAD efficaces, nous étudions les algorithmes de synthèse (système, architectures, controleur, datapath, architecture et système mémoire et IPs). Notre objectif est de mettre au point des outils de "preuve de concept" permettant de valider nos algorithmes sur des applications industrielles.

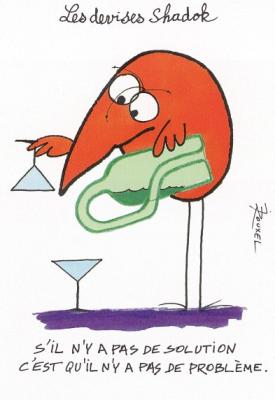

Philosophie

Research in Embedded Systems Design (ESD) addresses the various aspects of bridging the gap between the demands of new applications and available technology. Dr. Chavet with Students, the ESD concentration is designed to produce computer scientists with an increased awareness of the demands imposed on computers by the application domains which have traditionally been viewed as extrinsic to computer science. This application sensitivity will give students a unique advantage in the increasingly important area of integrated software/hardware computer and application systems and will prepare them to meet the challenges of real-world problems. The ESD research paradigm prepares our students to conceptualize a system design, prototype it and take it all the way to an efficient system implementation with the right balance of hardware and software components.