# Event management for large scale event-driven digital hardware spiking neural networks

Louis-Charles Caron<sup>a\*</sup>, Michiel D'Haene<sup>b</sup>, Frédéric Mailhot<sup>a</sup>, Benjamin Schrauwen<sup>b</sup>, Jean Rouat<sup>a</sup> <sup>a</sup> NECOTIS, Université de Sherbrooke, 2500 boul. de l'Université, Sherbrooke (Québec) Canada \* email: lcaron@ensta.fr <sup>b</sup> Reservoir Lab, Ghent University, Sint Pieternieuwstraat 41, 9000, Ghent, Belgium

## Event-driven approach to SNNs

Spiking neural networks (SNNs) can take many forms and involve various implementation strategies and optimizations. Two different approaches are widely used and opposed: time-driven (see Algorithm 1) and **event-driven** (see Algorithm 2) [1].

| Algo          | rithm 1 Time-driven implementation                  |                |

|---------------|-----------------------------------------------------|----------------|

|               | <b>_</b>                                            | Event-driven S |

| 1: <b>r</b> e | epeat                                               |                |

| 2:            | move one step forward in time                       | Time steps f   |

| 3:            | for each neuron in the network $\mathbf{do}$        | events         |

| 4:            | update state                                        | + no event =   |

| 5:            | end for                                             |                |

| 6: <b>u</b>   | ntil desired time is reached                        | + temporal p   |

|               |                                                     | Neurons invo   |

| Algo          | rithm 2 Event-driven implementation                 | updated        |

| 1: <b>r</b> e | epeat                                               | + few comp     |

| 2:            | move one event forward in time                      | ➢Inverse neur  |

| 3:            | for each neuron involved in the event $\mathbf{do}$ | - better with  |

| 4:            | update state                                        |                |

| 5:            | end for                                             | Need to iden   |

| 6:            | find next event to happen                           | to fire        |

| 7             | , • 1 1 · 1 · · 1 · · 1 1                           |                |

| 1: u          | ntil desired time is reached                        | - event man    |

# **FPGA** implementation

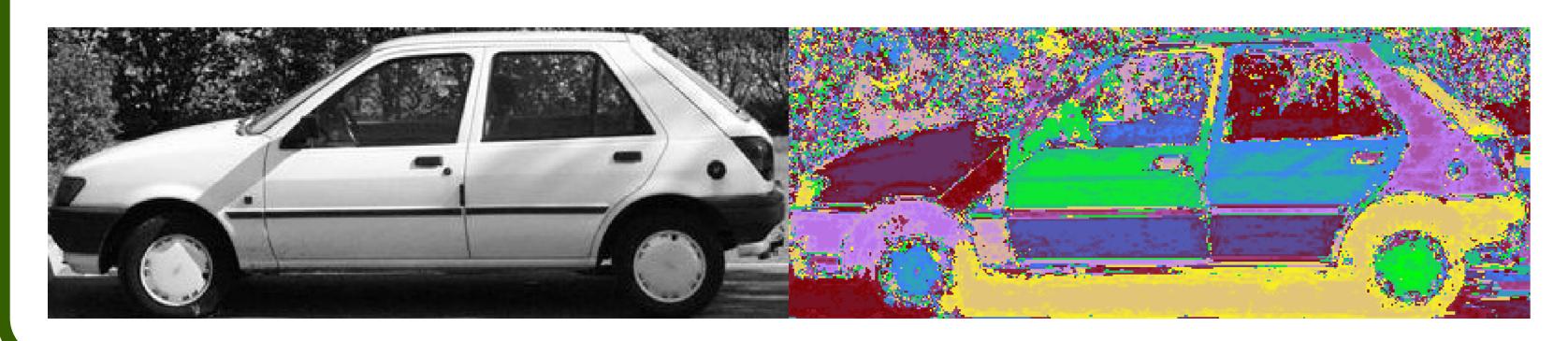

Image segmentation on Xilinx XC5VSX50T FPGA using the Oscillatory Dynamic Link Matcher (ODLM) signal processing SNN [6]. ➢ 65 536 neurons, 513 184 synapses network Segmentation of a 406×158-pixel image in 200ms @100MHz (takes)

1.9s on an Intel Core i5 @2.4GHz, 3GB RAM) ≻~1 250 000 events / second

SNNs fit the occurrence of

= no processing precision volved in an event are

## outations

ron model simple SNNs ntify the next neuron

## nagement

# Digital hardware event management

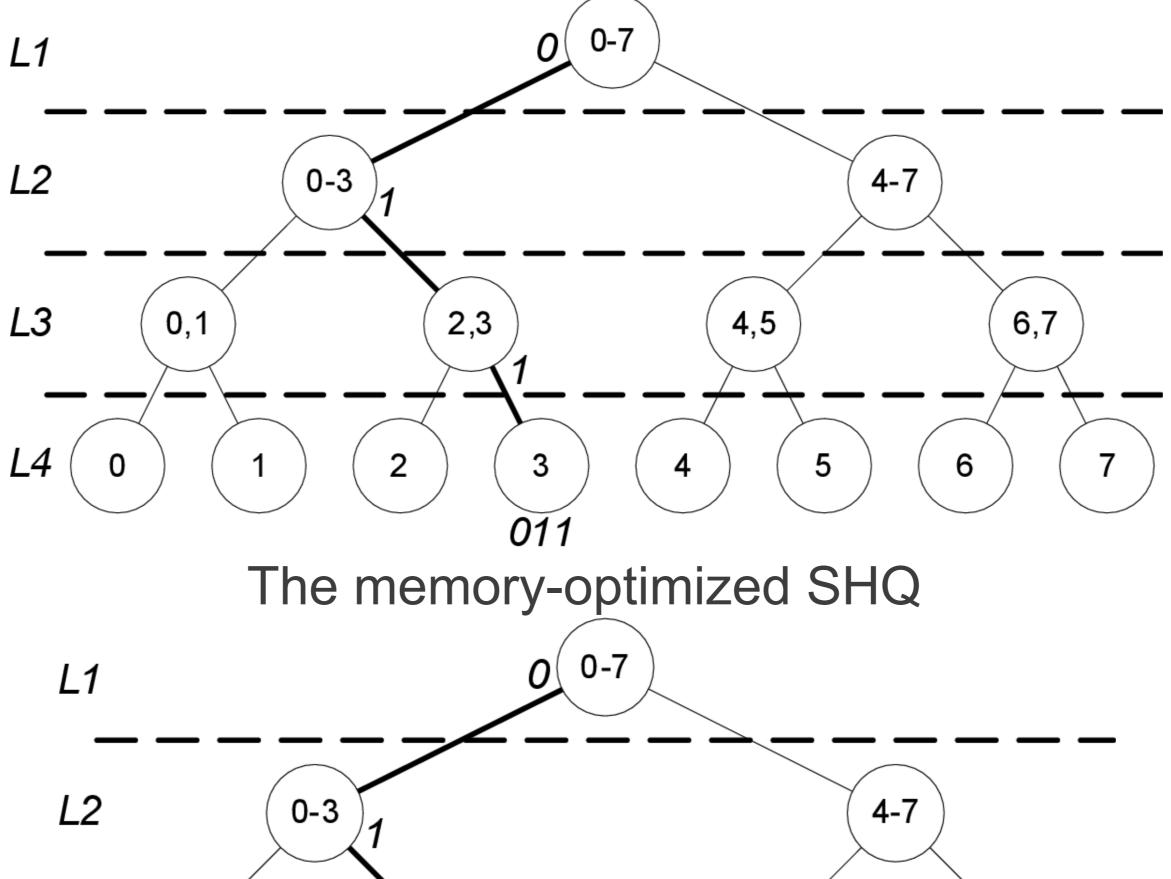

Most digital hardware SNNs implement a hybrid time- and event-driven system, without any form of event management, because hardware solutions for event management scale badly with the number of events. Similar to Agís et al. [2], we strictly follow the pattern of Algorithm 2, but our Structured Heap Queue (SHQ) [3] has O(1) complexity in time.

|                               | Method                    | Hardware                                                                                                                                                           |                                                    | Performance                                                            |

|-------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------|

|                               |                           | Memory                                                                                                                                                             | 2-input comparators                                | Clock cycles (cc)                                                      |

| Agís et al. [2]               | fly search for the next   | Memory array, with 256 read por<br><b>1 write port</b><br><b>33% less memory usage</b>                                                                             | rts and Pipelined comparator tree, 255 comparators | 10 cc with fewer than<br>2048 events, up to 69<br>cc with 16384 events |

| <b>Caron et al.</b><br>[3, 4] | (SHQ), a variation of the | <b>Binary memory tree with 2 read and</b><br><b>1 write ports per level (28 read ports comparators with 16384 events)</b><br>and 14 write ports with 16384 events) |                                                    | 7 clock cycles                                                         |

### FUNCTION

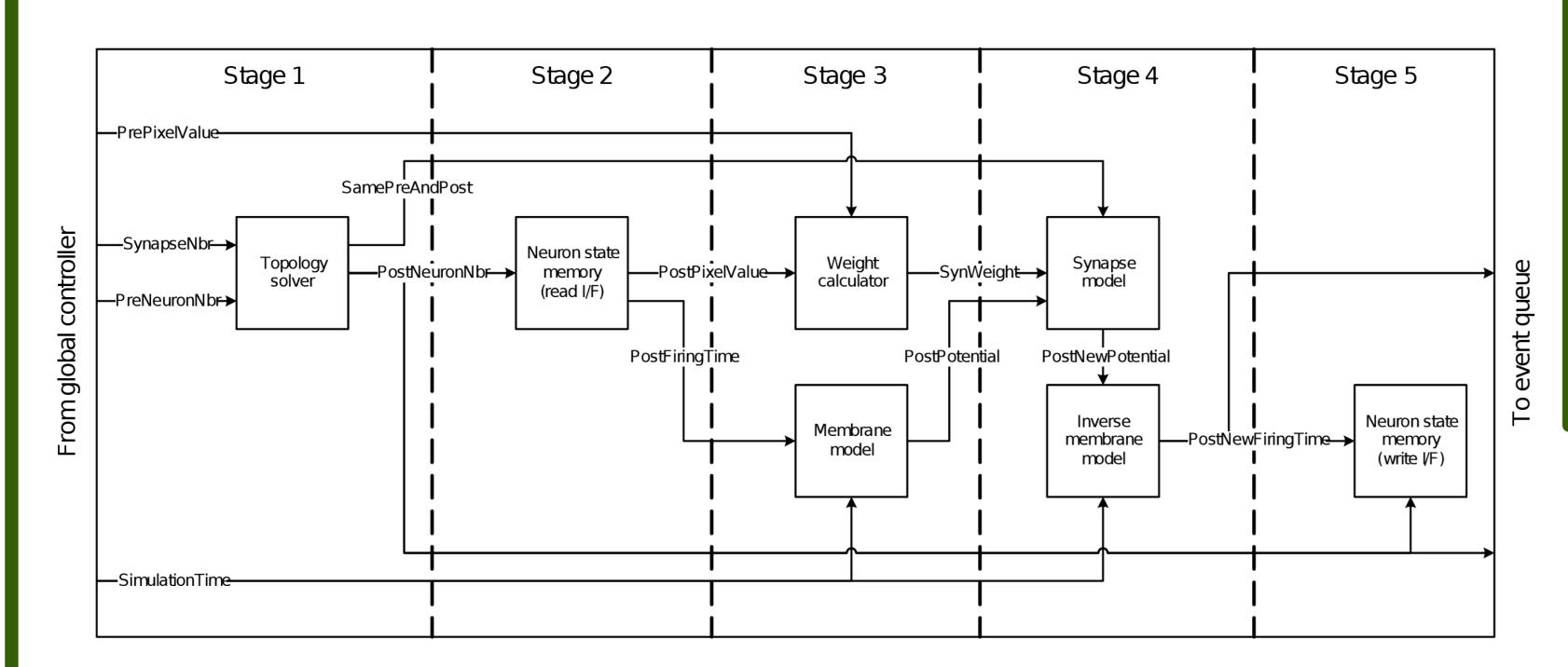

Controller Processing element Topology solver Neuron memory Weight calculator Membrane model Synapse model Inverse membrane model Event queue

# K

| $\mathbf{FFs}$ | $\mathbf{LUTs}$ | BRAMs |

|----------------|-----------------|-------|

| 503            | 635             | 0     |

| 19             | 73              | 50    |

| 16             | 26              | 0     |

| 1              | 1               | 44    |

| 0              | 8               | 0     |

| 1              | 14              | 3     |

| 0              | 10              | 0     |

| 1              | 14              | 3     |

| 846            | 3965            | 80    |

|                |                 |       |

# Scaling, with

Complexity in logic Complexity in memory Complexity in time for Delete top element Delete any element Insert Read top element Read any element

\*In (Agís et al., 2007),conversely, time for logic.

## Summary

Spiking neural network: use your own SNN Event-driven: save resources by only computing values you are interested in Digital hardware: tailor your system to your needs by trading logic for time and memory Structured heap queue: get a constant processing time, no matter the size of your SNN

[1] D'Haene, M. (2010). Ph.D. thesis. [2] Agís, R., Ros, E., Díaz, J., Carrillo, R., & Ortigosa, E. M. (2007). International Journal of Electronics, 94, 469–480.

[3] Rouat, J., Bergeron, J., Caron, L. C., de Ladurantaye, V., & Mailhot, F. (2012). WIPO Patent No. 2012167359. Geneva, Switzerland: World Intellectual Property Organization. [4] Caron, L. C., D'Haene, M., Mailhot, F., Schrauwen, B., & Rouat, J. (2013). Neural Networks, ISSN 0893-6080 10.1016/j.neunet.2013.02.005. [5] Ioannou, A., & Katevenis, M. G. H. (2007). IEEE/ACM Transactions on Networking, 15, 450-461.

[6] Pichevar, R., Rouat, J., & Tai, L. (2006). Neurocomputing, 69, 1837–1849.

| N the number of events |                     |  |  |  |  |

|------------------------|---------------------|--|--|--|--|

| $\mathbf{SHQ}$         | Agís et al. (2007)  |  |  |  |  |

| $O(\log(N))$           | $O(N)^*$            |  |  |  |  |

| y $O(N)$               | O(N)                |  |  |  |  |

| r                      |                     |  |  |  |  |

| O(1)                   | $O(\log(N))^*$      |  |  |  |  |

| O(1)                   | O(1)                |  |  |  |  |

| O(1)                   | O(1)                |  |  |  |  |

| O(1)                   | $O(\log(N))^*$      |  |  |  |  |

| $O(\log(N))$           | O(1)                |  |  |  |  |

| logic can be t         | raded for time, and |  |  |  |  |