Of Southampton ARM SIIISTIX THALES

## **SpinNaker** - a Biologically-Inspired Massively-Parallel Architecture

Alex Rast and Steve Furber The University of Manchester <u>rasta@cs.man.ac.uk</u> <u>steve.furber@manchester.ac.uk</u>

## **Bio-inspiration**

•How can massively parallel computing resources accelerate our understanding of brain function? •How can our growing understanding of brain function point the way to more efficient parallel, fault-tolerant computation?

#### Brains demonstrate

- massive parallelism (10<sup>11</sup> neurons)

- massive connectivity (10<sup>15</sup> synapses)

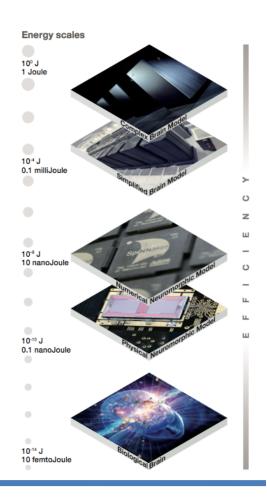

- excellent power-efficiency

- much better than today's microchips

- low-performance components (~ 100 Hz)

- low-speed communication (~ metres/sec)

- adaptivity tolerant of component failure

University Of

- autonomous learning

Southampton ARM SILISTIX THALES

DATE 22 Mar 2013

nspired Aassively arallel rchitectures

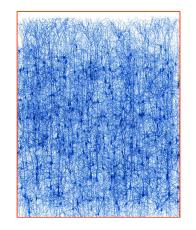

## **Building brains**

University Of

#### ·Neurons

- multiple inputs, single output (c.f. logic gate)

useful across multiple

- scales  $(10^2 \text{ to } 10^{11})'$

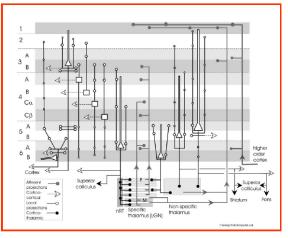

#### ·Brain structure

EPSRC

- regularity

- e.g. 6-layer cortical 'microarchitecture'

UNIVERSITY OF CAMBRIDGE

Southampton ARM SILISTIX THALES

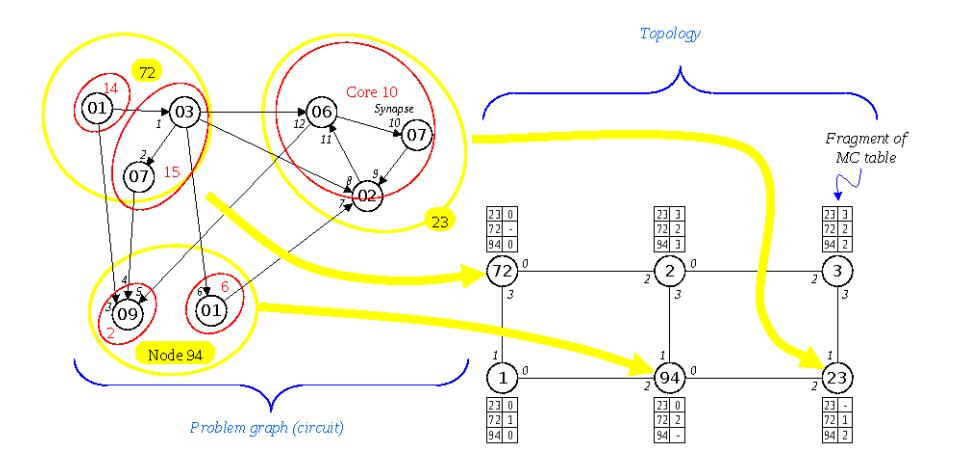

- ·Virtualised topology

- physical and logical connectivity are decoupled

- ·Bounded asynchrony

- time models itself

- •Energy frugality

- processors are free

- the real cost of computation is energy

University Of Southampton ARM SILISTIX THALES

DATE 22 Mar 2013 EPSR

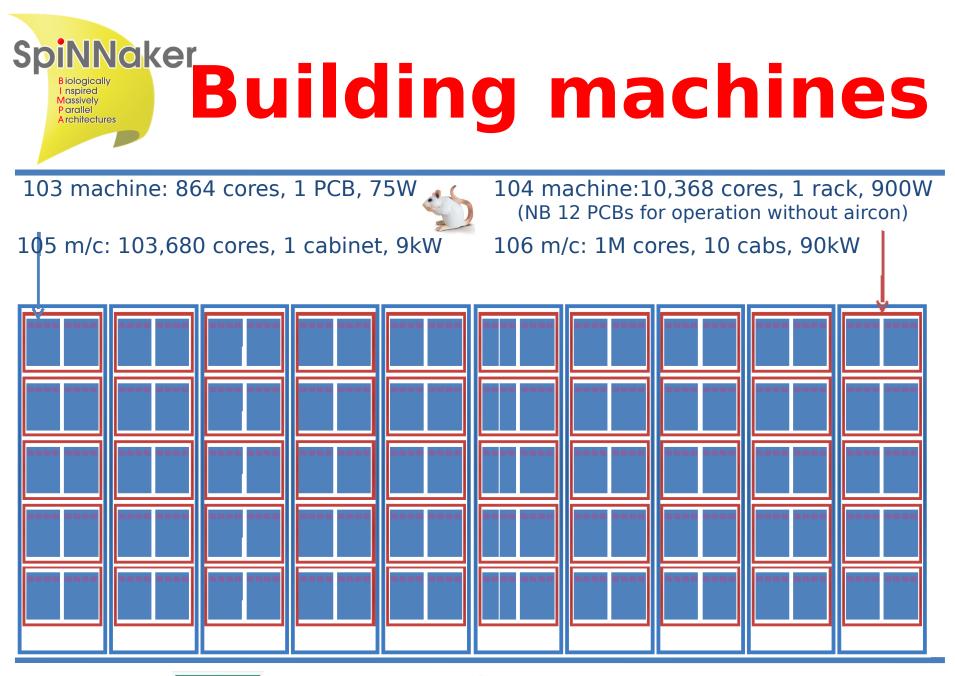

A million mobile phone processors in one computer

Able to model about 1% of the human brain...

...or 10 mice!

EPSRC

UNIVERSITY OF CAMBRIDGE

of Southampton ARM SILISTIX THALES

DATE 22 Mar 2013

Southampton ARM SILISTIX THALES

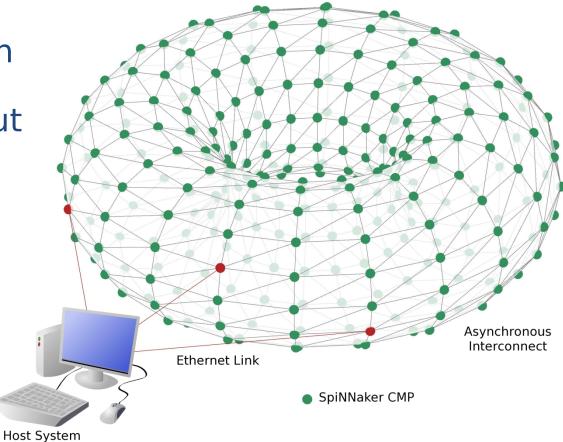

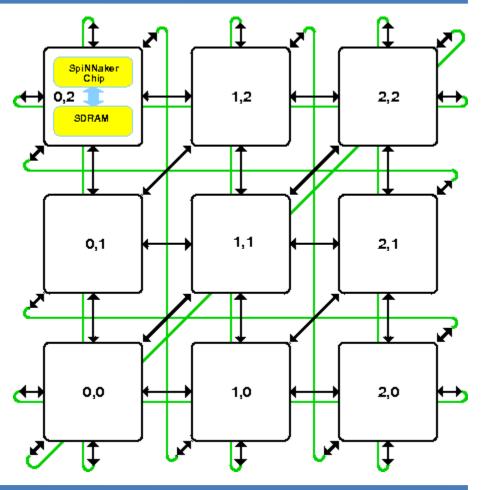

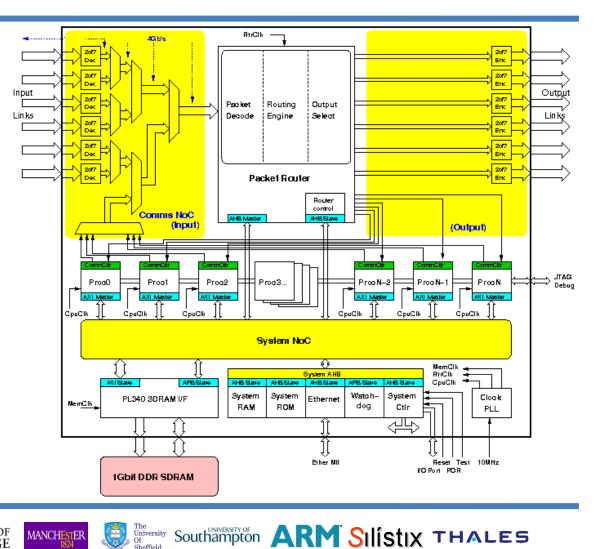

#### SpiNNaker system

University Of

•A packet-switched, toroidal hexagonal grid of chips

•A routable network with virtual topology

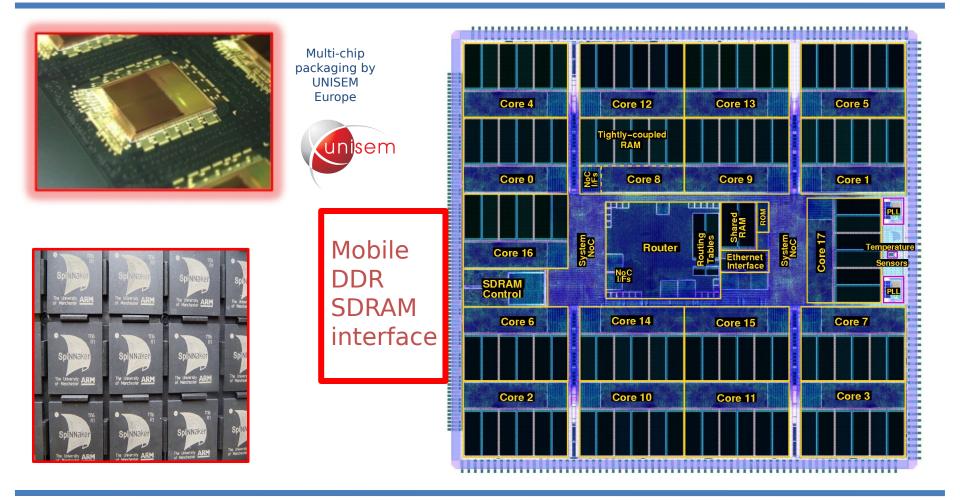

•Each chip: 16 Application Cores, 1 Monitor, 1 Spare

•Each package: SpiNNaker die + SDRAM

EPSR

UNIVERSITY OF CAMBRIDGE

Southampton ARM SIIISTIX THALES

## SpiNNaker node

University Of

·Native parallelism

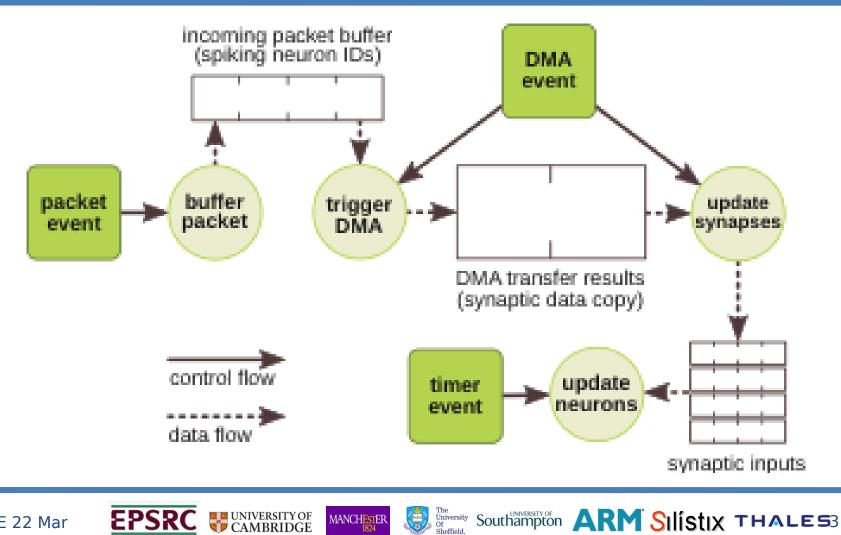

·Event-driven Processing

Distributed **Incoherent Memory**

EPSRC

UNIVERSITY OF CAMBRIDGE

Incremental Reconfiguration

#### SpiNNaker chip

Southampton ARM SILISTIX THALESO

University Of

Sheffield

DATE 22 Mar 2013

EPSRC

UNIVERSITY OF CAMBRIDGE

DATE 22 Mar 2013

EPSRC

# Spinnake Biologically Massively Parallel Parallel

University Of

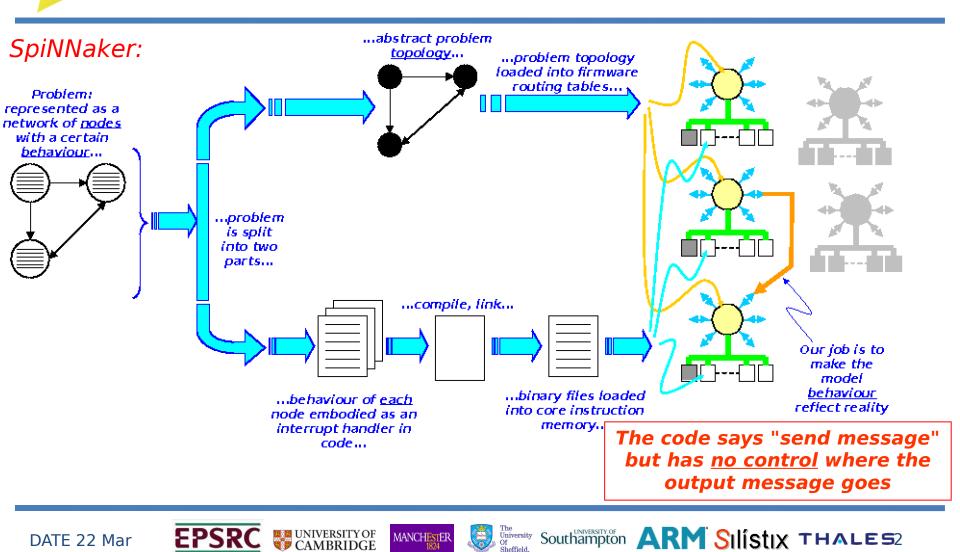

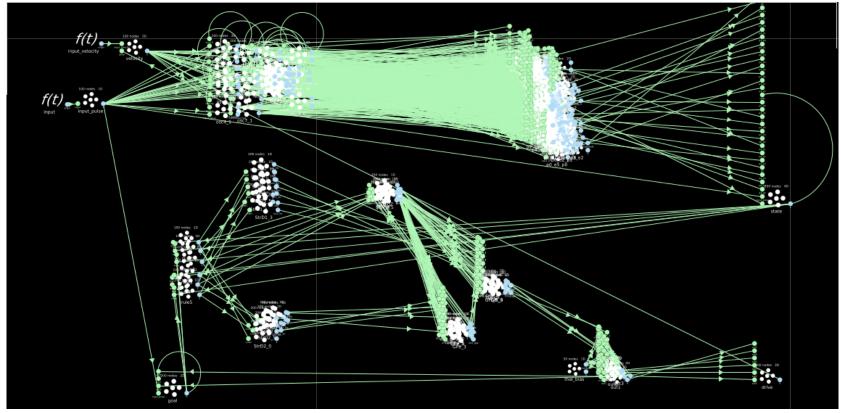

#### **Event-driven software model**

#### Spinner Biologically Nassively Paralle Architectures

University Of

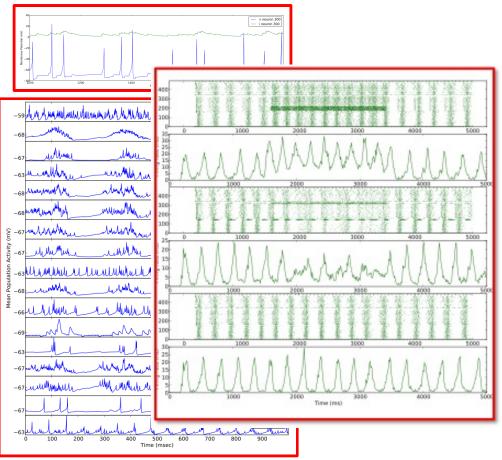

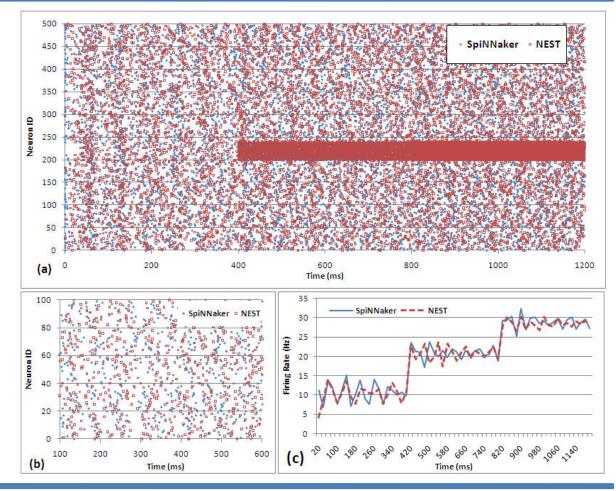

Vogels Abbott

benchmark

- 500 LIF

neurons

EPSRC

UNIVERSITY OF CAMBRIDGE

Southampton ARM SILISTIX THALES

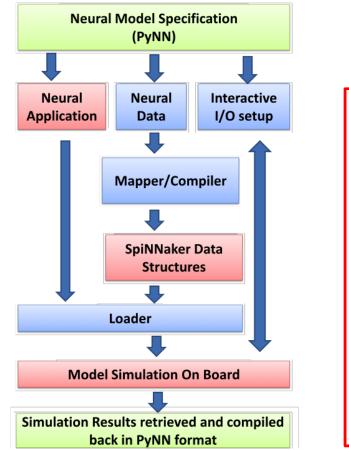

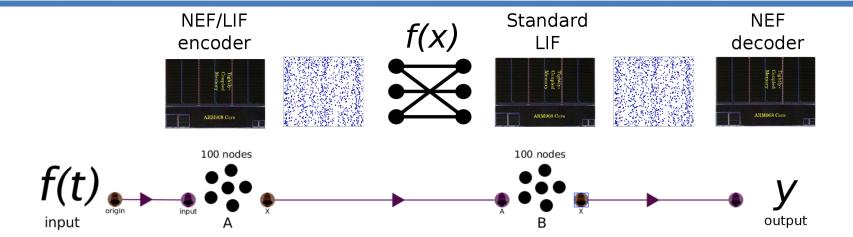

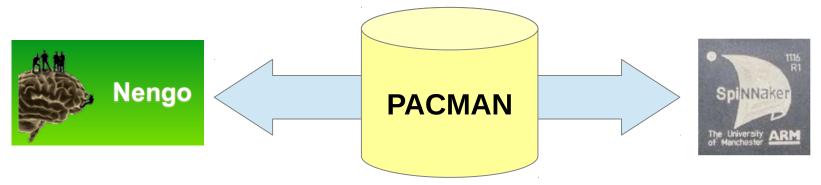

•Models are written in Nengo and automatically translated into SpiNNaker data structure by PACMAN. Real time interaction using Nengo

UNIVERSITY OF CAMBRIDGE

EPSRC

University Of Southampton ARM SIISTIX THALES

#### NENGO Spiking ratSLAM

University of Southampton ARM Silistix THALES7

·13910 neurons in 230 populations - 670 SpiNNaker cores ·4806500 synapses in 1601 projections - 40-100 Hz firing rate

DATE 22 Mar 2013

EPSRC

UNIVERSITY OF CAMBRIDGE

### Spaun

a)

·SpiNNaker: 5M conn/s/ARM ·Spaun: · 2.5M neurons ~100Hz firing rates ~500 inputs/neuron · 125G conn/s ·Real-time Spaun: · 25,000 ARMs · 30x 48-node PCB

UNIVERSITY OF CAMBRIDGE

by end 2013?

EPSRC

Chris Eliasmith et al, Science vol. 338, 30 Nov 2012

Action Selection

of Southampton ARM SILISTIX THALES

DLPFC

VLPEC

Decoding

= hierarchy

## Conclusions

University Of

•Brains represent a significant computational challenge

- now coming within range?

- •SpiNNaker is driven by the brain modelling objective

- virtualised topology, bounded asynchrony, energy frugality

- •The major architectural innovation is the multicast communications infrastructure •We have working hardware

- · 48-node 864-ARM PCBs now

- first multi-PCB systems now working

Southampton ARM SIIISTIX THALES