### Demonstration: Emulation environment of a DVB-S2 decoder

CNRS, UMR 6285, Lab-STICC Centre de Recherche - BP 92116 F-56321 Lorient Cedex - FRANCE

RÉPUBLIQUE FRANÇAISE MINISTÈRE DE L'ENSEIGNEMENT SUPÈRIEUR ET DE LA RECHERCHE

- Interaction Algorithm Architecture" team of Lab-STICC/pole CACS, develops jointly algorithm and associated architecture to optimize overall cost.

- For the physical layer, the quality is measured in term of Bit Error Rate (BER) and the complexity in terms of area, time to design and power dissipation.

- ♦ Optimization is a very complex task since:

- ♦ Many parameters to optimize;

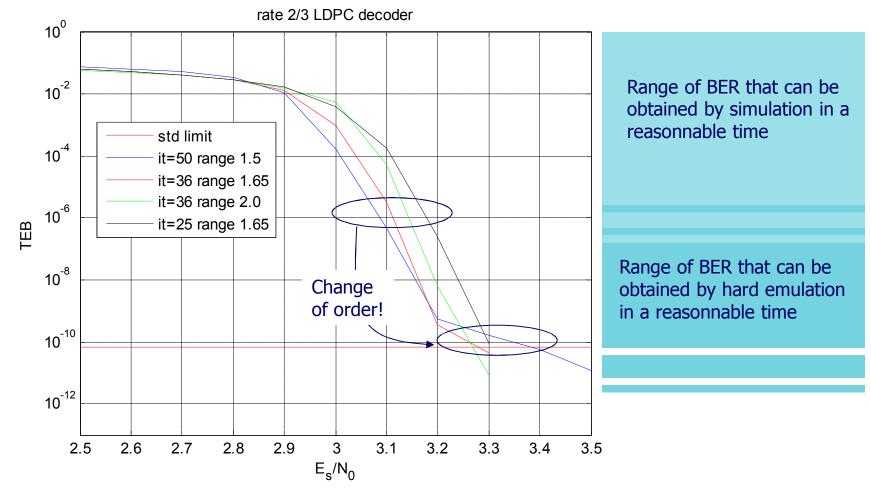

- Evaluation of performance requires heavy Monte-Carlo simulations, for example, determining at which level of signal to noise ratio a LDPC decoder architecture is compliant with the DVB-S2 standard requires the simulation of more than 10 000 000 000 bits !

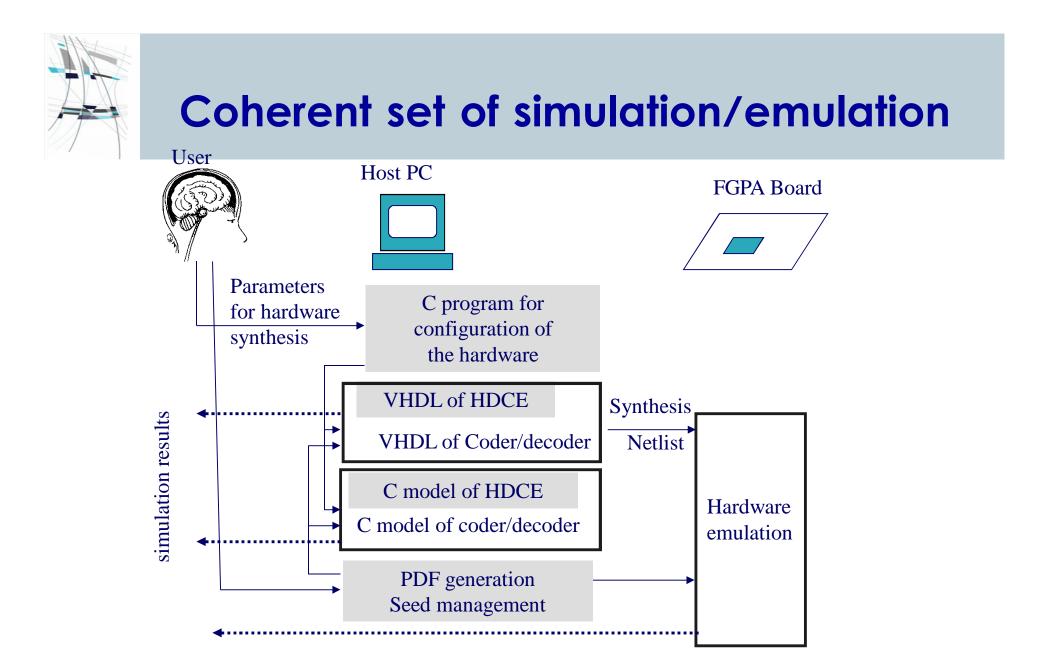

# Solution developed in the Frame of PALMYRE II

♦ In order to reduce Monte-Carlo simulation, we can:

- ♦ Exploit also the soft information of a Monte-Carlo simulation [1]

- ♦ Reduce the number of Monte-Carlo simulation to be run [2]

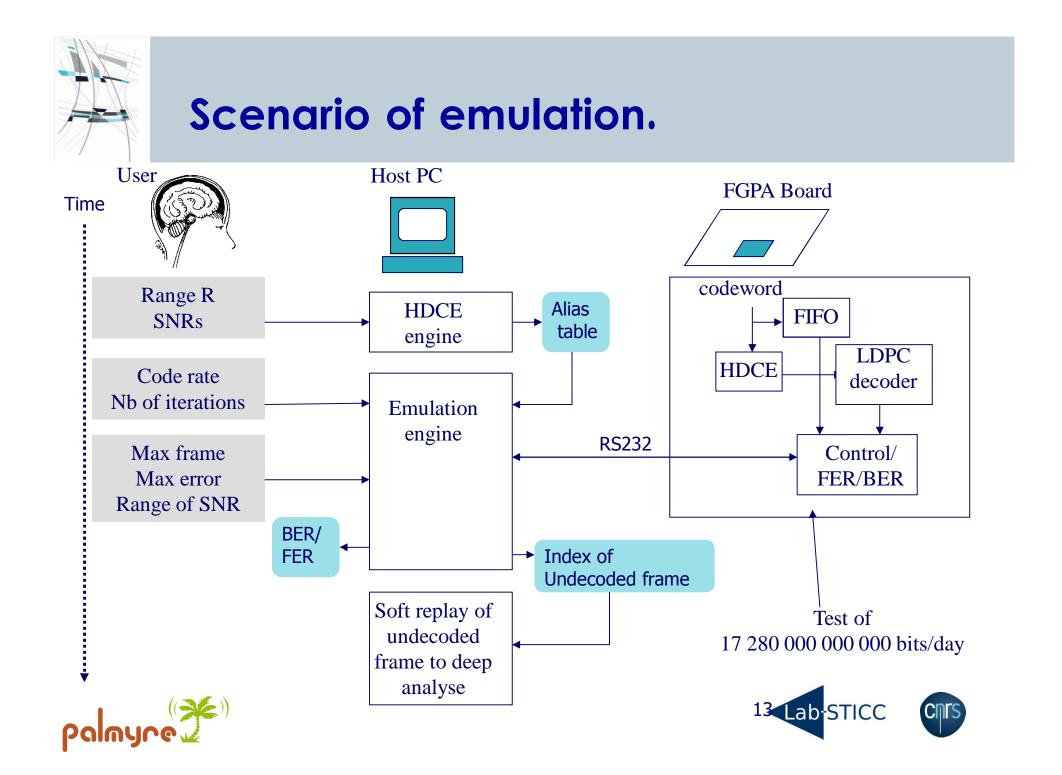

- Speed up the Monte-Carlo simulation, replacing CPU based simulation by FPGA based emulation.

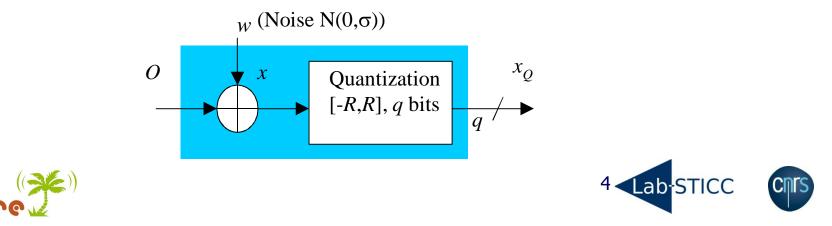

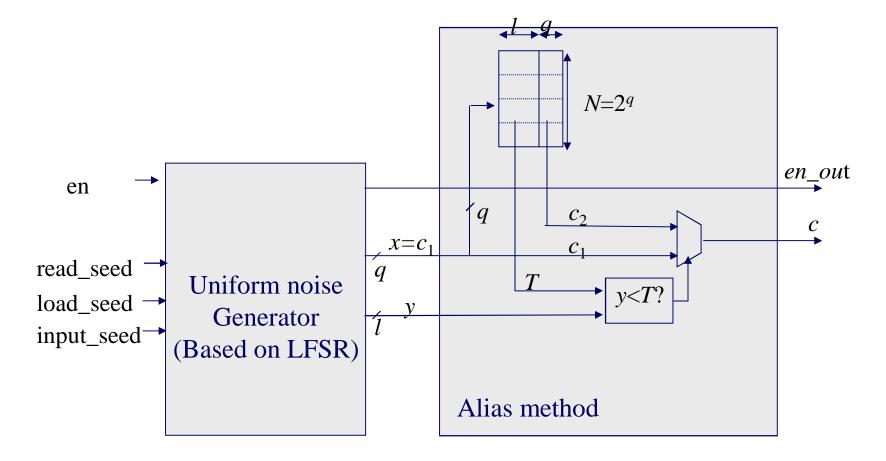

#### The last item required to emulate also the channel: Hardware Discrete Channel Emulator [3].

- [1] A. Singh, A. Al-Ghouwayel1, G. Masera, E. Boutillon, "<u>A New Performance Evaluation Metric for</u> <u>Sub-Optimal Iterative Decoders</u>", IEEE Communications letters, vol. 13, n°7, pp. 513-515, July 2009.

- [2] E. Boutillon, C. Douillard, G. Montorsi, "<u>Iterative Decoding of Concatenated Convolutional Codes:</u> <u>Implementation Issues</u>", Transactions of the IEEE, vol. 95, n°6, june 2007.

- [3] E. Boutillon, Y. Tang, C. Marchand, P. Bomel, "Hardware Discrete Channel Emulator", The 2010 International Conference on High Performance Computing & Simulation (HPCS 2010), pp 452-458, Caen, June 2010..

Paln

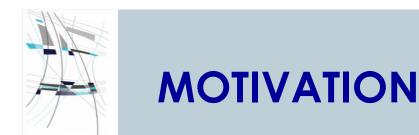

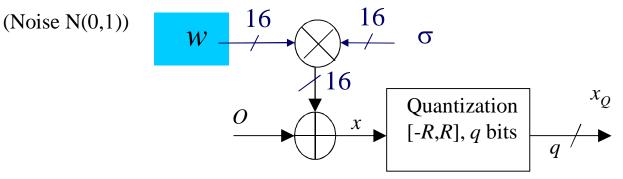

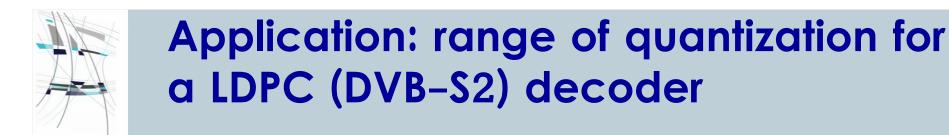

#### • Straigth method: Direct emulation of the AWGN channel.

• New method: emulate channel + quantization.

• FOR A GIVEN x,  $\sigma$  and R,  $y_Q$  is EQUIVALENT TO A DISCRETE R.V.

# Principle of generation of a discrete random variable.

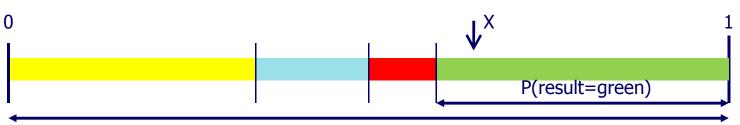

#### • 1D method

Oraw a random number between [0,1] and see where it falls

(Discrete random variable with *N*=4 values, represented by color)

- Complex to implement: the value x needs to be compared to all the thresholds (*N*-1 comparizons).

- Solution : go toward 2D.

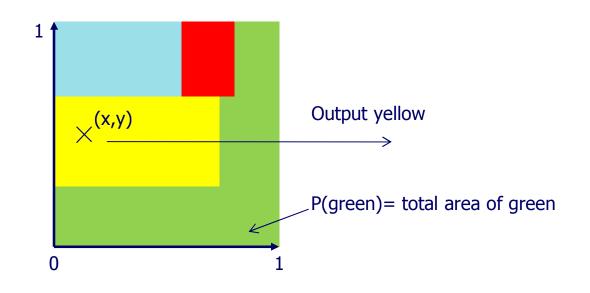

## Principle of generation of a discrite random variable.

o 2D method

Principle: generate two random variables x,y between [0,1] and see where they fall.

♦ No simplification => need a structure.

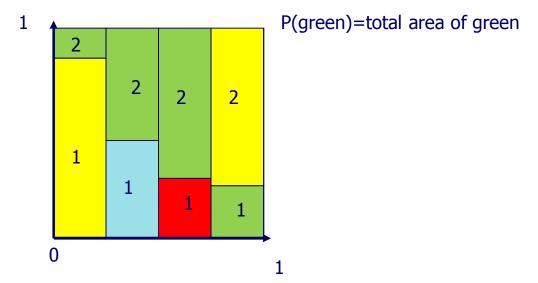

# Principe of generation of a discrite random variable.

2D method: with x, select a column, with y, select color 1 or 2 in the column.

♦ X: random number between 1 to N to select color 1 (*c*<sub>1</sub>), then, read color 2 (*c*<sub>2</sub>) and the threshold *T* in a memory and compare *y* to *T* to select *c*<sub>1</sub> or *c*<sub>2</sub>.

- June 2011-March 2012: Design of a DVB-S2 LDPC decoder for a Korean company (Private contract).

- Innovation: using "vertical scheduling" instead of "horizontal scheduling".

- Size: 64 800 bits, rate 1/2 and 2/3 (proof of concept).

- Decoding throughput: 200 Mbit/s (information bit) with 36 decoding iterations on a Xilinx Virtex 5.

### Demonstration...

### After few days of simulations...

- Methods to optimized error control code architecture using both simulation and emulation.

- So far, methods applied for:

- ♦ NXP (CIFRE): LDPC DVB-S2 (schedul. horizontal).

- Orange Labs (private contract): Code cortex

- ETRI (Private contract): LDPC DVB-S2 (schedul. Vertical)

- ♦ DaVinci (FP7): LDPC Non Binaire.