# Quelques aspects de la réalisation matérielle d'un décodeur *LDPC*

# François VERDIER David DECLERCQ Jean-Marc Philippe

« Equipes Traitement des Images et du Signal » ETIS

UMR CNRS 8051

http://www.etis.ensea.fr

F. Verdier

## Quelques aspects de la réalisation matérielle d'un décodeur *LDPC*

- 1.Les codes *LDPC*

- 2. La classe des codes congruents réguliers

- 3. Architecture et parallélisation du décodeur

- 4. Conséquences du calcul en précision finie

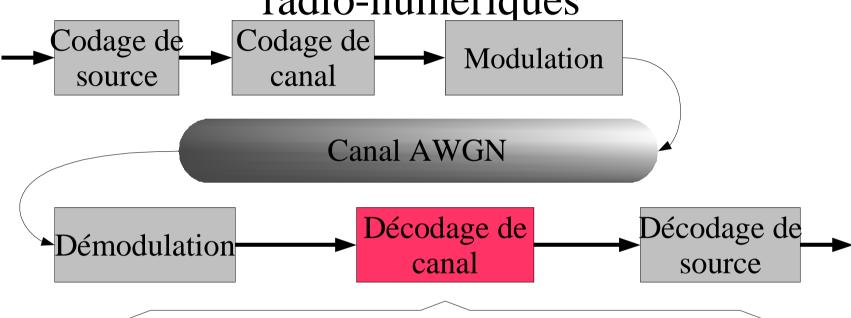

1. Les codes *LDPC* dans les transmissions radio-numériques

- Codes « blocs » à vérification de parité de grande taille (10<sup>4</sup> à 10<sup>6</sup>)

- Canaux fortement bruités (RSB = qq dB)

- Débits importants (> Msymb./sec.)

- Rendements variables

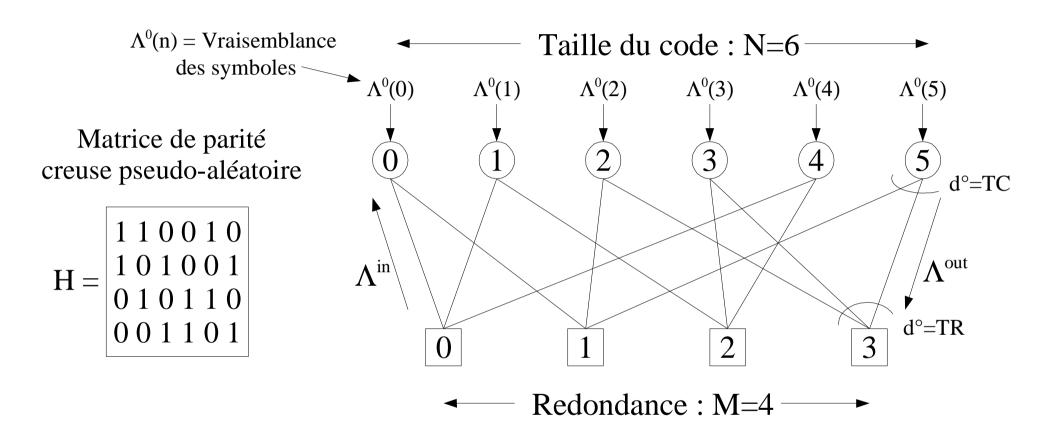

### Représentation graphique d'un code LDPC

$\Lambda^{\text{in}}$  et  $\Lambda^{\text{out}}$  : messages échangés sur les branches

Code LDPC régulier (6,4,2,3) de rendement ½

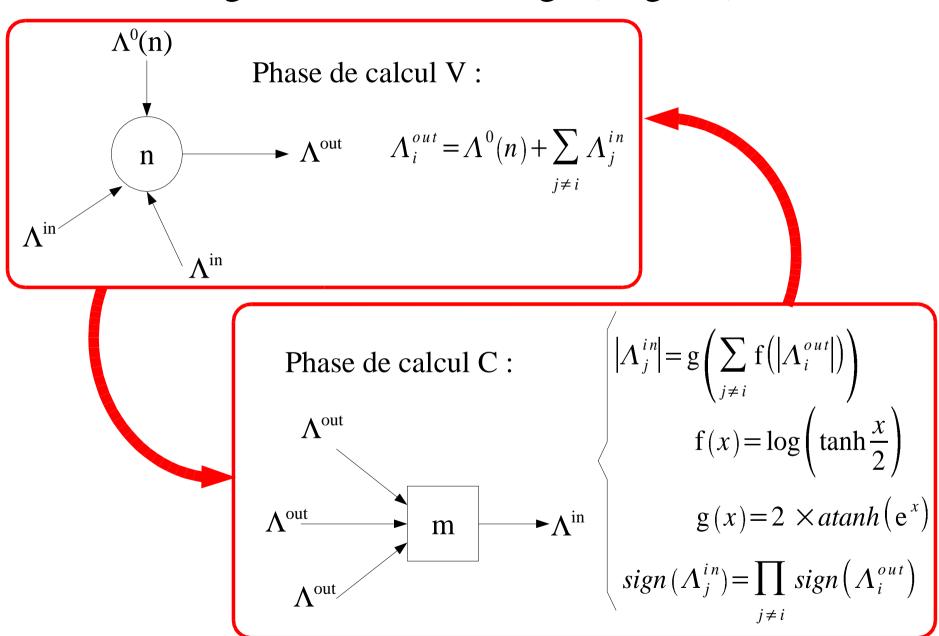

#### Algorithme de décodage (Log-BP)

## Problème d'Adéquation Algorithme / Architecture

Matrice de décodage pseudo-aléatoire  $\longrightarrow$  Codage ? Stockage ? Codes de grande taille ( $10^4$  à  $10^6$ )  $\longrightarrow$  Grande quantité de mémoire Taille de code variable  $\longrightarrow$  Parallélisation / scalabilité ?

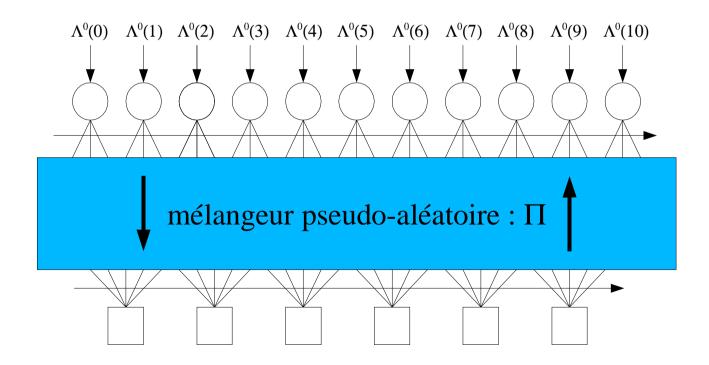

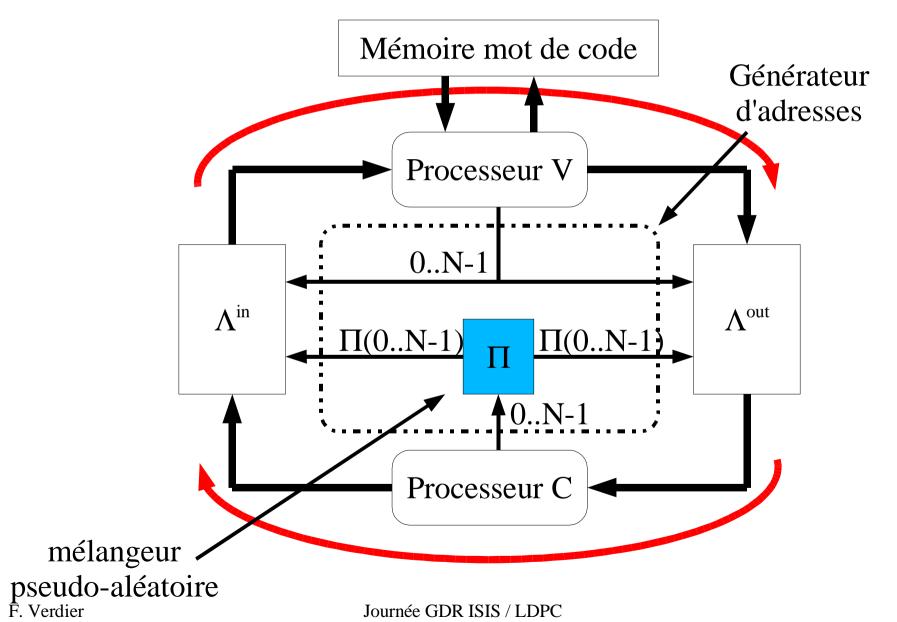

## Impact architectural du code pseudo-aléatoire

Les messages  $\Lambda^{in}$  et  $\Lambda^{out}$  sont stockés en mémoire Les branches sont parcourues séquentiellement dans l'ordre naturel

Parcours des branches / parcours des adresses ?

## Solution proposée :

19/12/2002

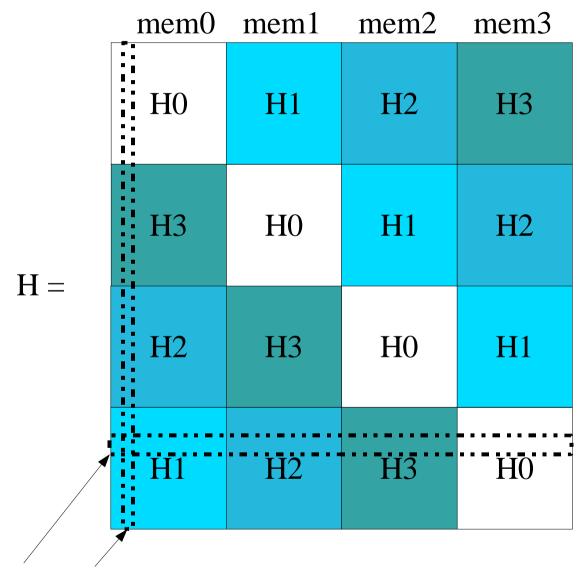

# 2. Une classe de codes facilement implantables : les codes congruents

- Le caractère pseudo-aléatoire de la matrice de décodage est incompatible avec un stockage ou un calcul simple des adresses des messages

- → Adresses calculées par un générateur congruent et récursif [Prabhakar2002]

- → Pas de stockage de la matrice

- → Paramétrage simple du générateur congruent

$$\Pi_{n+1} = (a \times \Pi_n + b) mod(N_b)$$

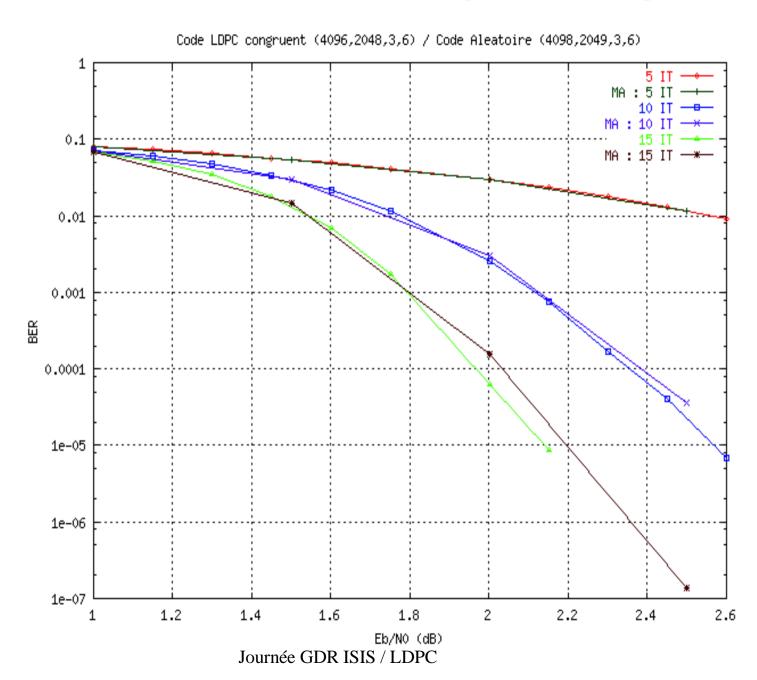

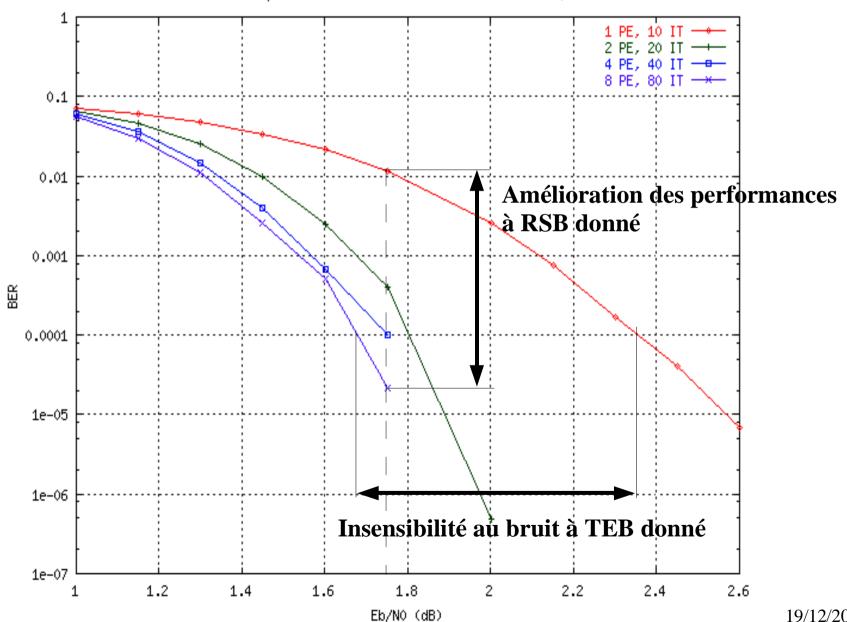

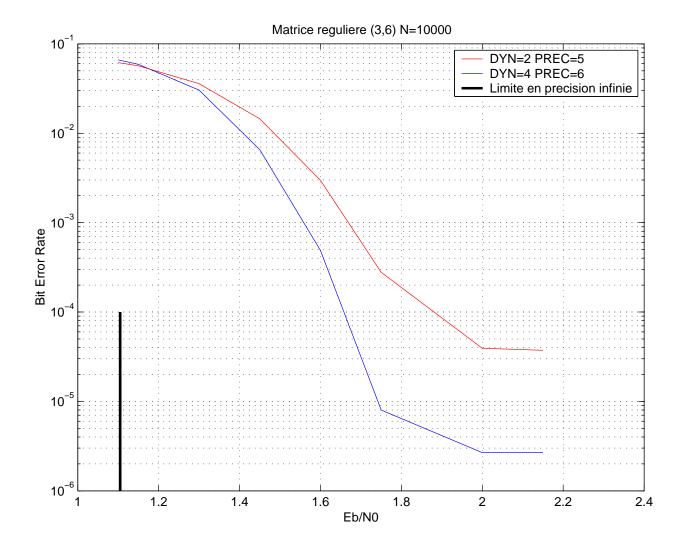

## Performances des codes congruents réguliers :

## 3. Architecture du décodeur

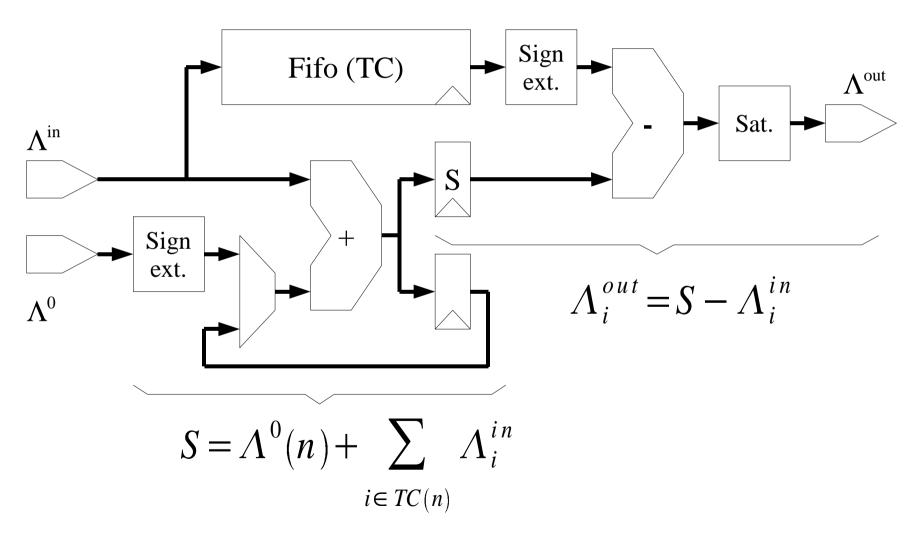

## 3.1) Implantation pipeline du processeur V

F. Verdier

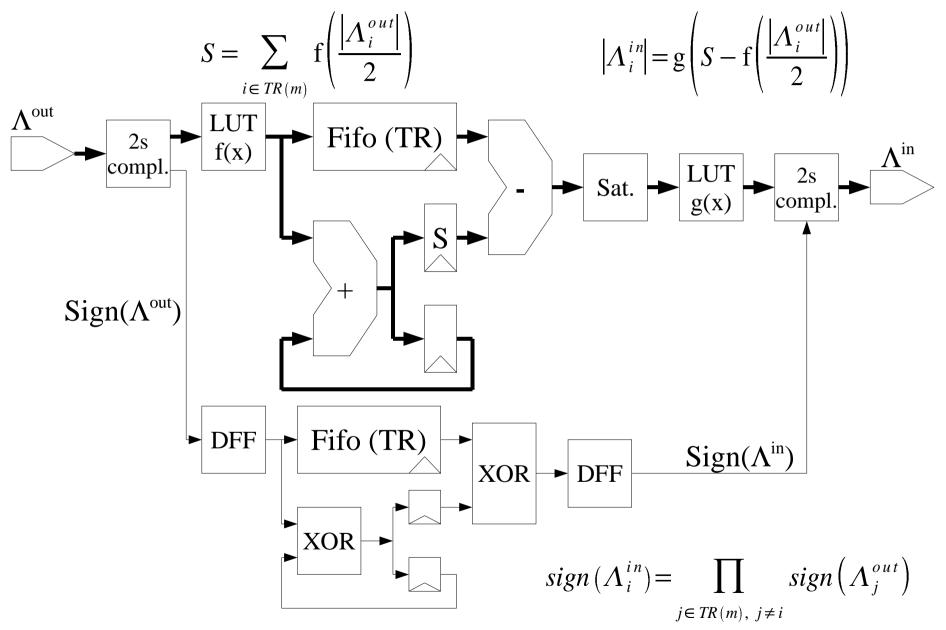

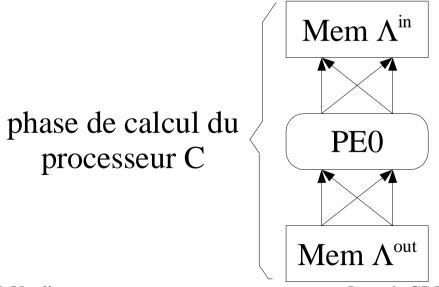

## 3.2) Implantation pipeline du processeur C

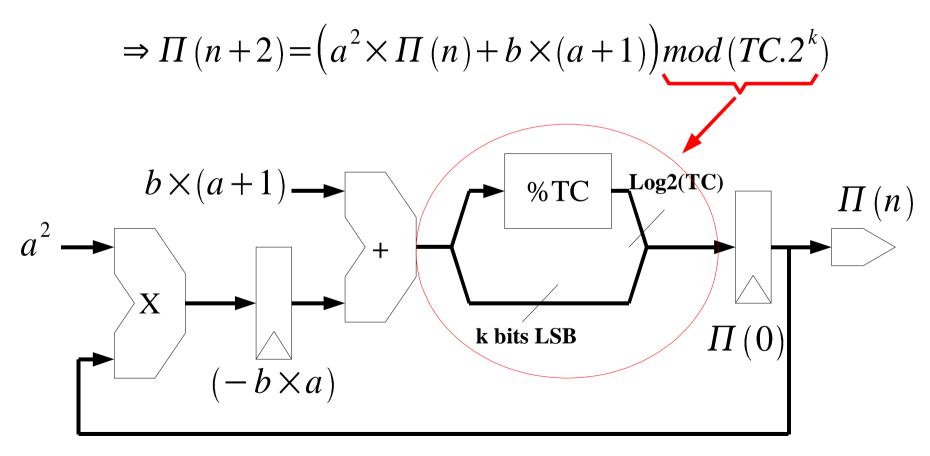

## 3.3) Implantation du générateur congruent

Implantation pipeline du générateur pseudo-aléatoire récursif :

$$\Pi(n+1) = (a \times \Pi(n) + b) mod(N_b)$$

Impossible en 1 cycle à 100Mhz!

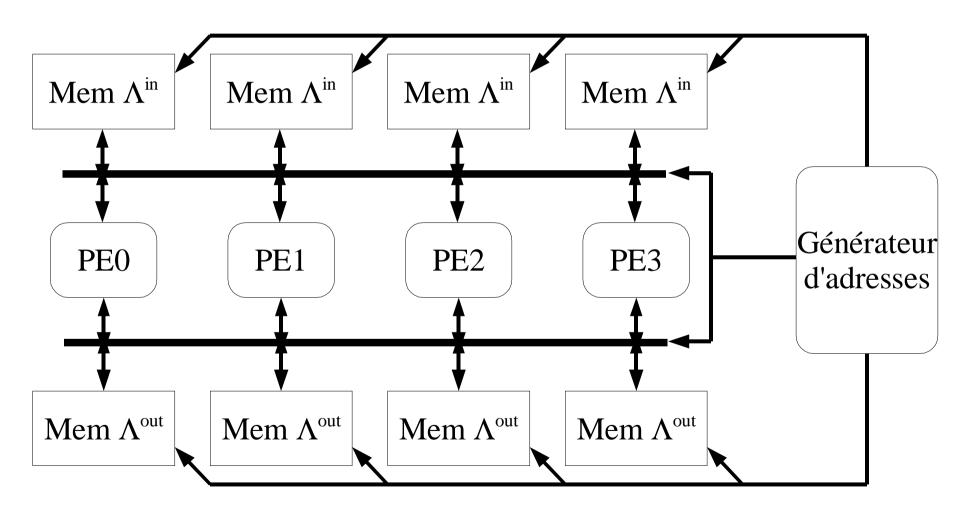

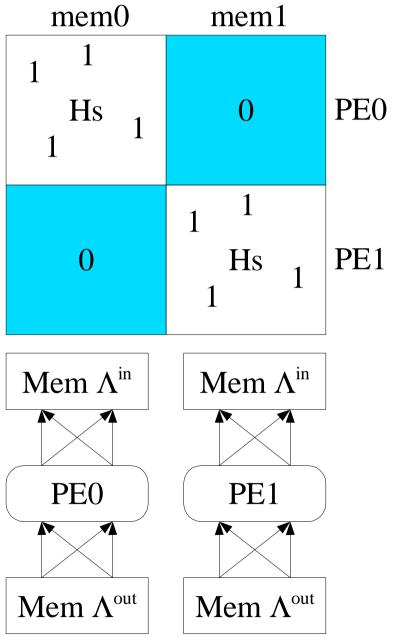

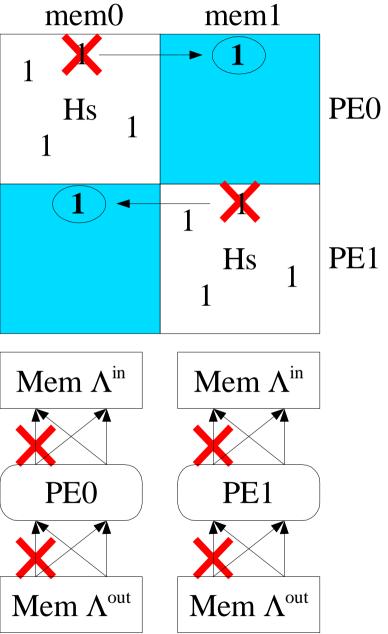

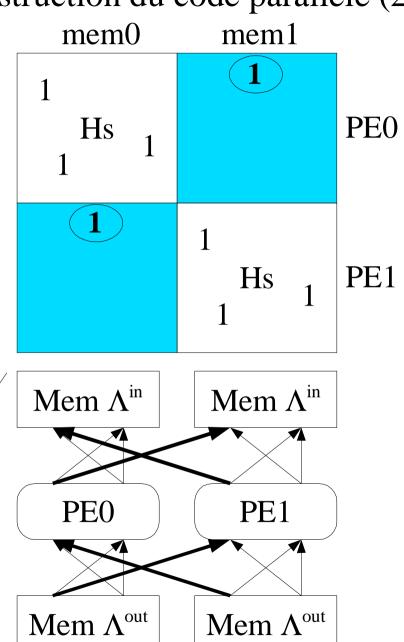

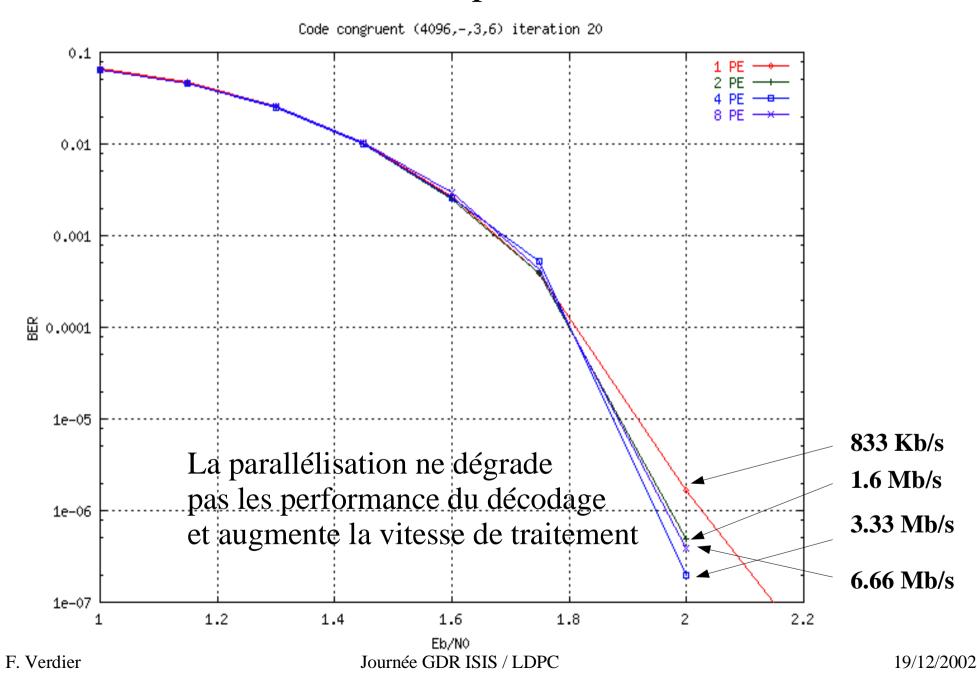

## Parallélisation du décodage

Processeurs parallèles synchrones + 2 réseaux de routage

F. Verdier

F. Verdier

Création des branches

inter-partitions

Journée GDR ISIS / LDPC

Le code reste régulier

#### Effets de la parallélisation

#### Effets de la parallélisation

Effet de la parallelisation a debit constant (615 us / 100 Mhz)

# 4. Conséquences du calcul en précision finie...

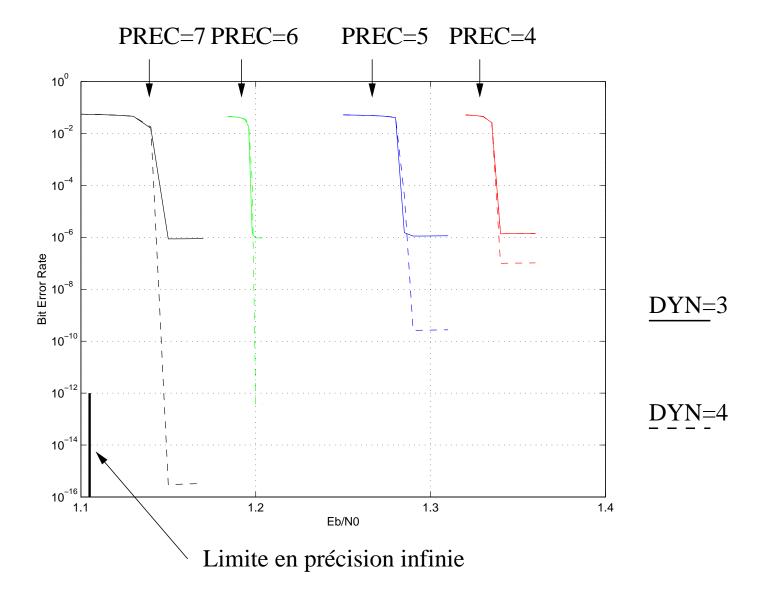

# Conséquences du Codage en Précision Finie

David Declercq<sup>†</sup> & Francois Verdier<sup>†</sup>

ETIS ENSEA/UCP/CNRS-8051

6, avenue du Ponceau 95000 Cergy-Pontoise

declercq@ensea.fr

<sup>†</sup> Dans le cadre de l'action JemSTIC CNRS

#### Conséquences du Codage en Précision Finie

#### Problèmes posés :

- □ Quantification des messages.

- □ Quantification des LUT.

- ⇒ Peut-on prévoir l'effet sur les performances du code.

- dégradation des performances,

- apparition d'un plancher de convergence.

Outil statistique : évolution de la densité de probabilité des messages au cours des itérations.

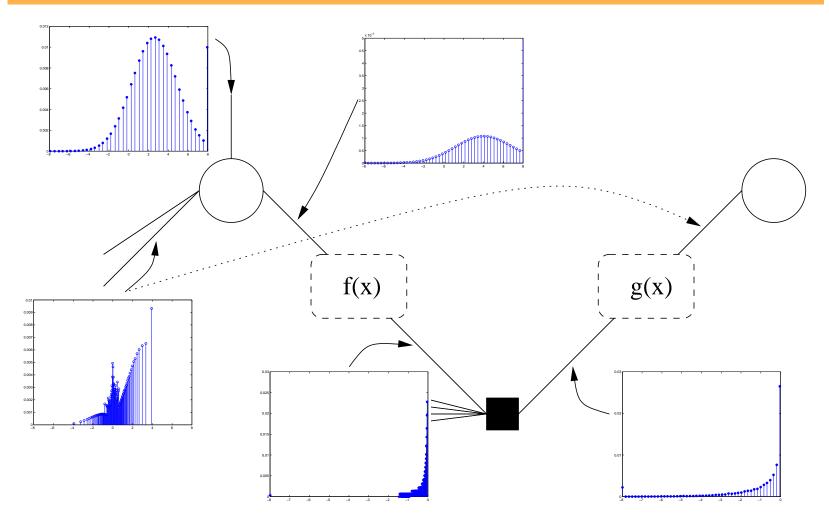

#### Evolution de Densité

$$f(x) = \log \tanh\left(\frac{|x|}{2}\right)$$

$g(x) = 2 \tanh^{-1} \exp(x)$

#### Hypothèses de travail

DYN : nombre de bits codant la partie entière

PREC : nombre de bits codant la partie fractionnaire

$$\{\Lambda_0(\omega),\Lambda_{in}(\omega),\Lambda_{out}(\omega)\}$$

$\Rightarrow$  V.A. discrètes à support dans  $\left[-DYN + \frac{1}{2^{PREC}} : \frac{1}{2^{PREC}} : DYN - \frac{1}{2^{PREC}}\right]$   $\left\{f\left(\Lambda_{in}(\omega)\right), f\left(\Lambda_{out}(\omega)\right)\right\}$

$\Rightarrow$  V.A. discrètes à support dans  $\left[-DYN + \frac{1}{2^{PREC}}: \frac{1}{2^{PREC}}:0\right]$

Fonction  $f(x) = \log \tanh\left(\frac{|x|}{2}\right)$

Fonction  $g(x) = 2 \tanh^{-1} \exp(x)$

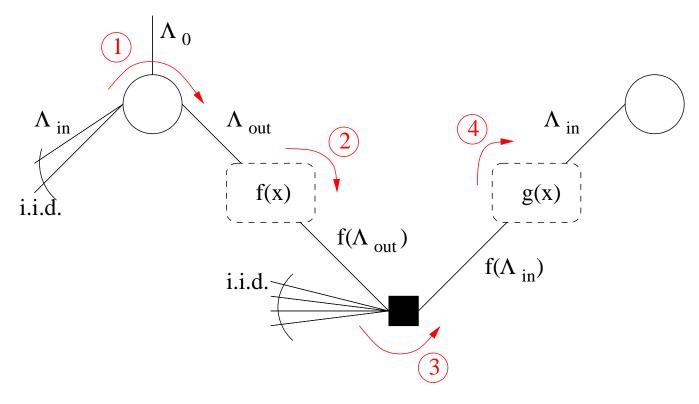

#### EVOLUTION DES DENSITÉS POUR 1 ITÉRATION

$$\boxed{1} \ \Lambda_{out} = \Lambda_0 + 2 \Lambda_{in}$$

$$\Rightarrow p\left(\Lambda_{out}\right) = p\left(\Lambda_{0}\right) * p\left(\Lambda_{in}\right) * p\left(\Lambda_{in}\right)$$

$$2 f(\Lambda_{out}) = \log \tanh\left(\frac{|\Lambda_{out}|}{2}\right)$$

⇒ Changement de variable + quantification.

$$\Rightarrow p\left(f\left(\Lambda_{in}\right)\right) = p\left(f\left(\Lambda_{out}\right)\right)^{*5}$$

$$\boxed{4} \Lambda_{in} = 2 \tanh^{-1} \exp(f(\Lambda_{in}))$$

⇒ Changement de variable + quantification.

#### FORME DES DENSITÉS

#### CONCLUSION ET PERSPECTIVES

- (1.) Modèle de parallélisation des codes LDPC.

- □ architecture simple et scalable,

- □ stockage du graphe de façon congruente,

- □ méthode de parallélisation sans dégradation de performances.

- 2.) Parallélisme pour les codes LDPC irréguliers

- □ problèmes de stockage du graphe,

- □ effets de la précision finie.