# Architecture FPGA Générique pour décodeur LDPC

F. Guilloud – J.-L. Danger – E. Boutillon

GDR ISIS

Journée LDPC du 19 décembre 2002

Telecom Paris

### Plan de la Présentation

- Une méthode sous-optimale du calcul des valeurs extrinsèques.

- L'influence de la quantification (entière) sur le décodage.

- Architecture : introduction

- Présentation d'une architecture « générique ».

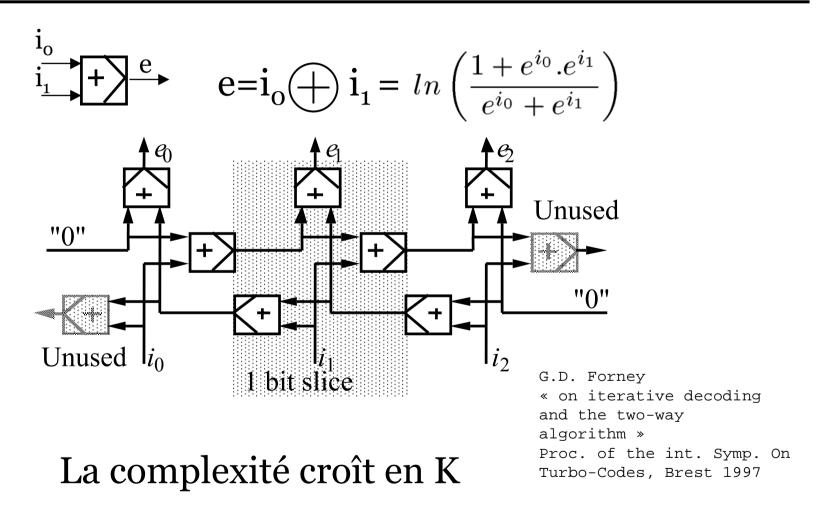

# Calcul sous-optimal des LLR extrinsèques

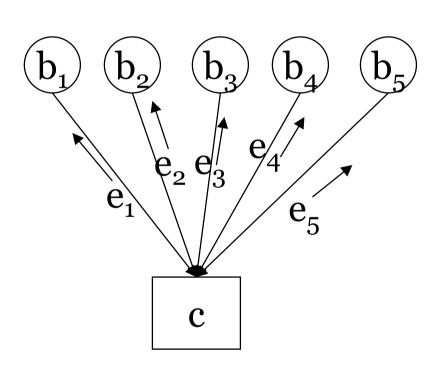

- Calcul des  $e_i : e_i = \bigoplus_{\substack{j \neq i \\ 1 < j < 5}} (b_j)$

- Observation:

les b<sub>j</sub> de faible amplitude ont plus de poids.

- Idée:

On ne calcule les e<sub>i</sub> qu'avec les N (ou N-1) b<sub>i</sub> minimum.

Exemple:

$$N = 3$$

: et  $b_1 < b_2 < b_3 < autres  $b_i$ :  $e_i = \bigoplus_{\substack{j \neq i \\ 1 < j < 3}} (b_j)$$

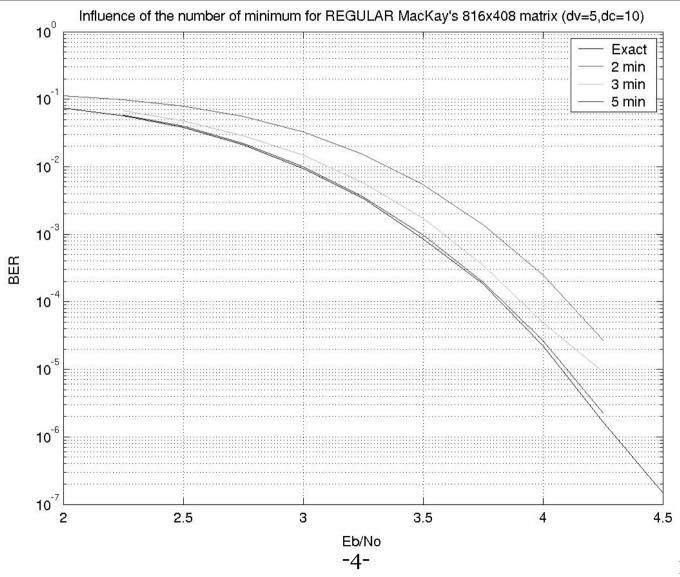

### **Simulations**

supérieure des

# Influence de la Quantification Entière

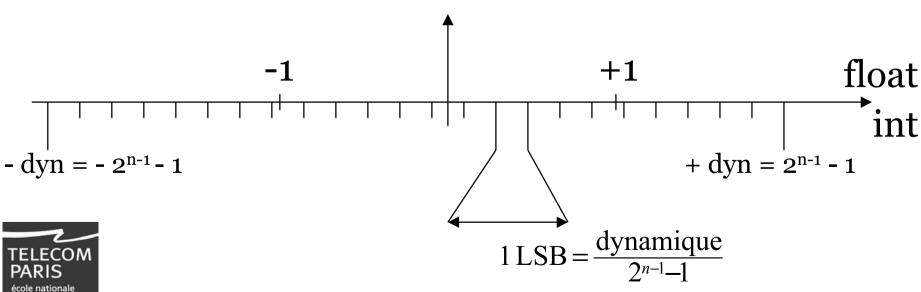

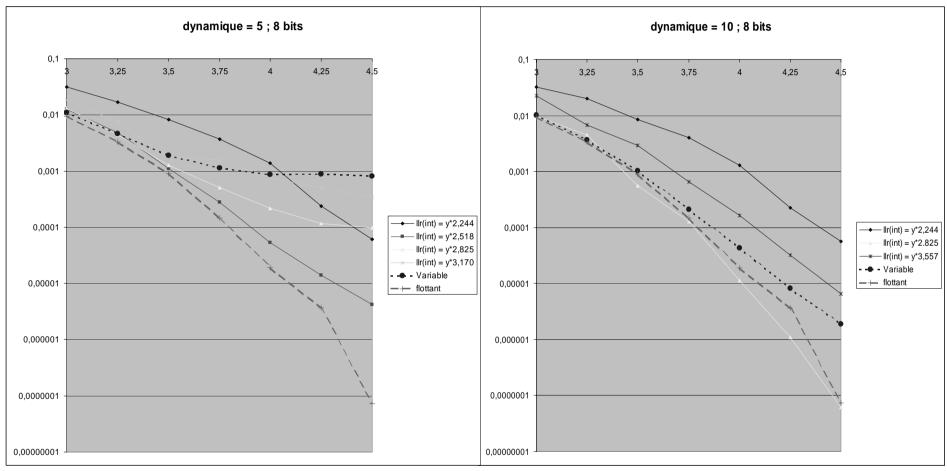

- 2 choix à faire :

- ⇒ Nombre de bit : n

- ⇒ Valeur d'un LSB, ou de la dynamique (i.e. la pleine échelle)

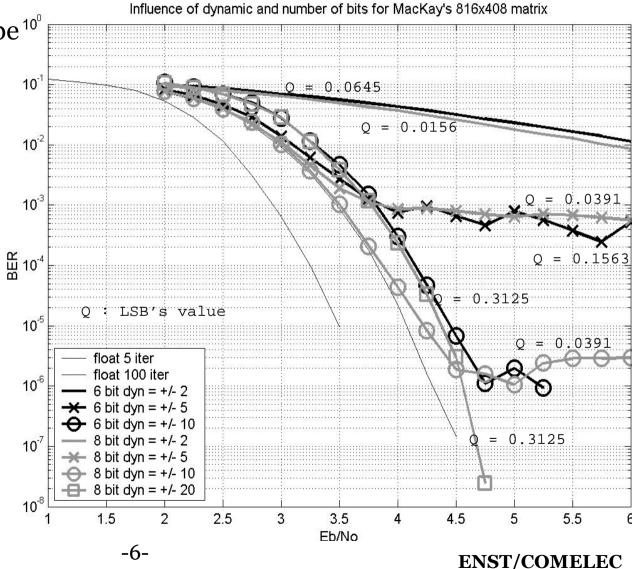

### Simulations

- Éloignement de la courbe <sup>10°</sup> réelle : il diminue si la valeur du LSB diminue.

- Effet de « seuil » : il est d'autant plus bas que la dynamique est grande.

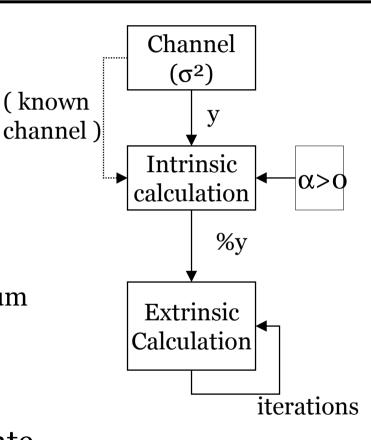

LLR intrinsèque =  $2y/\sigma^2$   $var(y) = \sigma^2 \Rightarrow$  $var(LLR intrinsèque) = <math>4/\sigma^2$

### Solutions

- On ne connaît pas le canal :

- $\Rightarrow LLR(intrinsèque) = \alpha.y \text{ où } \alpha = cste$   $\Rightarrow var(LLR intrinsèque) = \alpha^2 \sigma^2$

- On connaît le canal

- ⇒ Mettre une grande dynamique

- Il faut alors un nombre de bit élevé pour ne pas trop diminuer le quantum

- □ LLR(intrinsèque) =  $\alpha$ .y où  $\alpha$  = 2/ $\sigma$ <sup>2</sup> ⇒ var(LLR intrinsèque) = 4/ $\sigma$ <sup>2</sup>

- ⇒ Rendre var(LLR intrinseque) constante

- □ LLR(intrinsèque) =  $\alpha$ .y/ $\sigma$ ⇒ var(LLR intrinsèque) =  $\alpha$ <sup>2</sup>

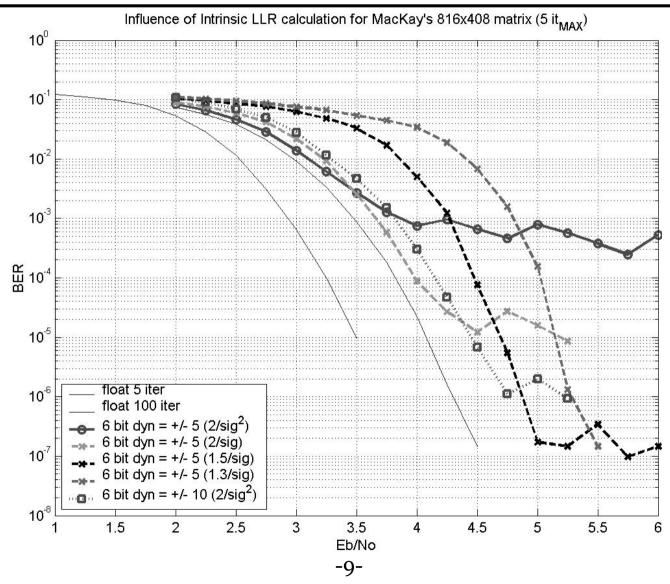

# Si on ne connaît pas le canal (Simulations)

**Constant** :  $llr(y) = \alpha.y$

**Variable**:  $llr(y) = 2y/\sigma^2$

# Si on divise par $\sigma$ (Simulations)

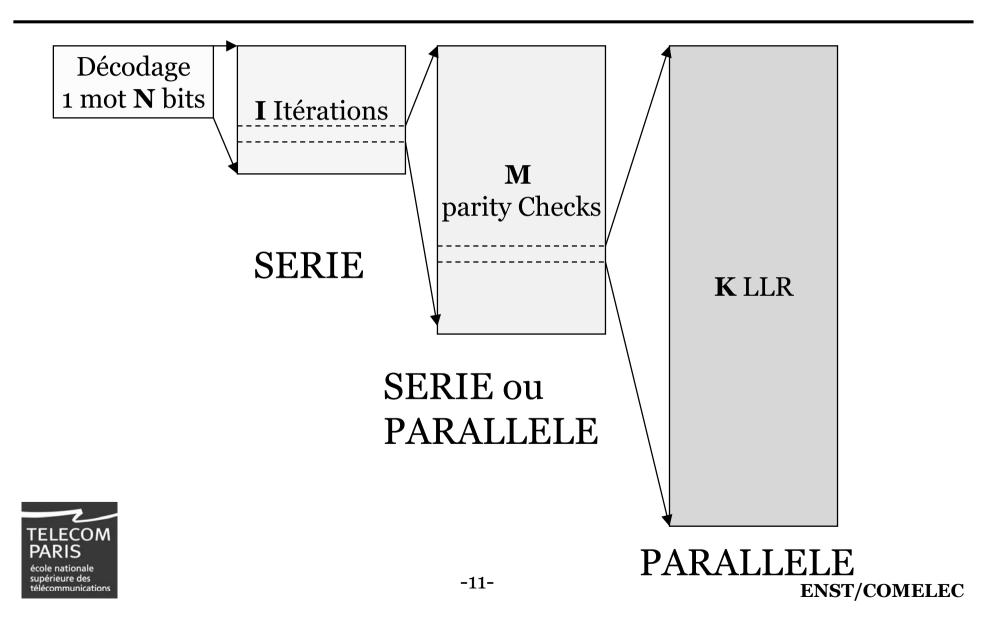

### Architecture: Introduction

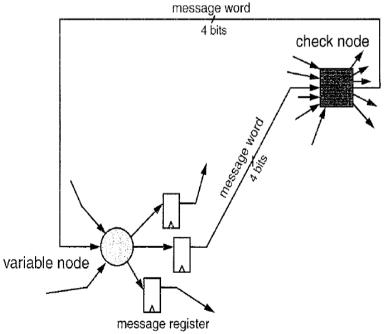

# Graphe des calculs

# Architecture parallèle

#### • Exemple

⇒ Blanksby, Howland, « A 690-mW 1-Gb/s 1024-b Rate-1/2 Low-Density Parity-Check Code Decoder » (IEEE Trans. on Solid-State Circuits, 2002.)

#### Avantages

- ⇒ performances : 1Gb/s 64 itérations

- ⇒ consommation : 690mW

- $\Rightarrow$  PER=2 10<sup>-4</sup> @ 2,5 dB

#### Inconvénients

- ⇒ Routage (2.k.M.B= 26624 equipotentielles, développement d'un outil de CAO ad hoc)

- ⇒ code figé

- ⇒ taille : 52.5mm² en techno 0.16μ

## Architecture « Decoder-first »(1)

#### Exemple

⇒ Boutillon, Castura ,

Kshishang « Decoder-First

Code Design », Proc. of the

2nd Int. Symp. on Turbo

Codes and Related Topics,

Brest, 2000.

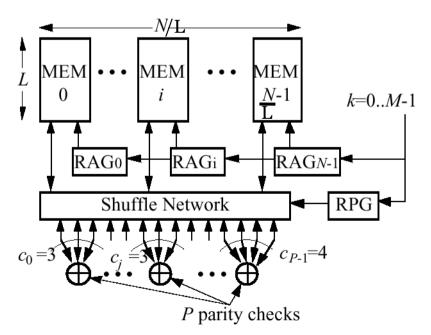

- Une architecture faisable et simple est d'abord conçue :

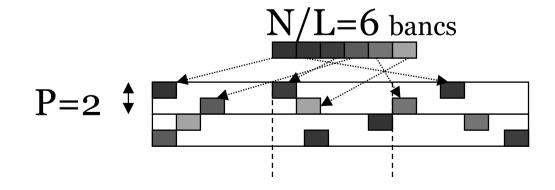

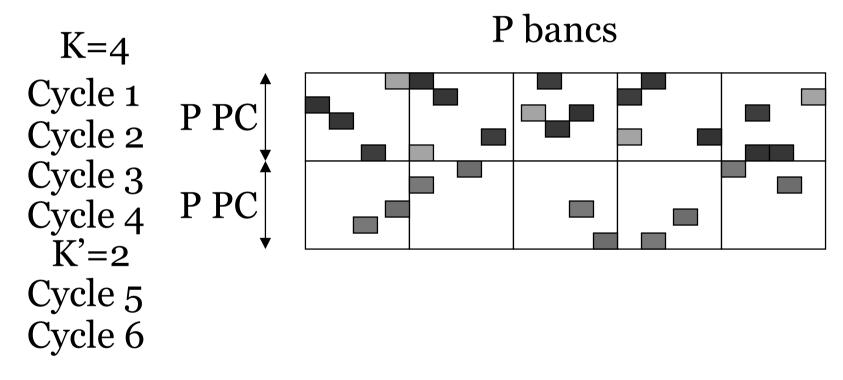

- ⇒ Architecture semi-parallèle : P

Parity Checks sont calculés simultanément

- ⇒ Les mémoires intrinsèques et extrinsèques sont organisées en N/L bancs :

- ⇒ N/L bits parmi N sont utilisés pour les P Parity Checks

- L'accès aux bancs et aux PC se fait à l'aide de générateurs de variables pseudoaléatoires

# Architecture « Decoder-first »(2)

#### • Avantages :

- ⇒ facilité d'implémentation

- ⇒ programmabilité des permutations

#### • Inconvénients :

- ⇒ contraintes sur la matrice

- ⇒ poids moyen k des PC = N/(L.P)

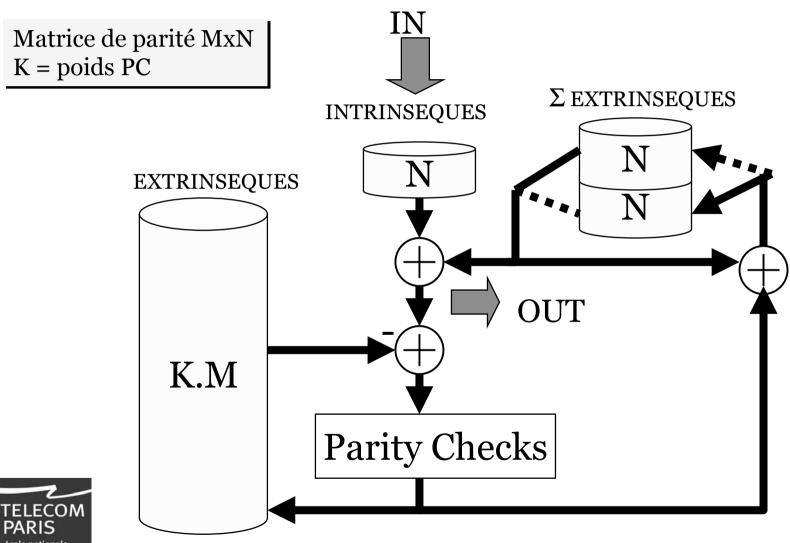

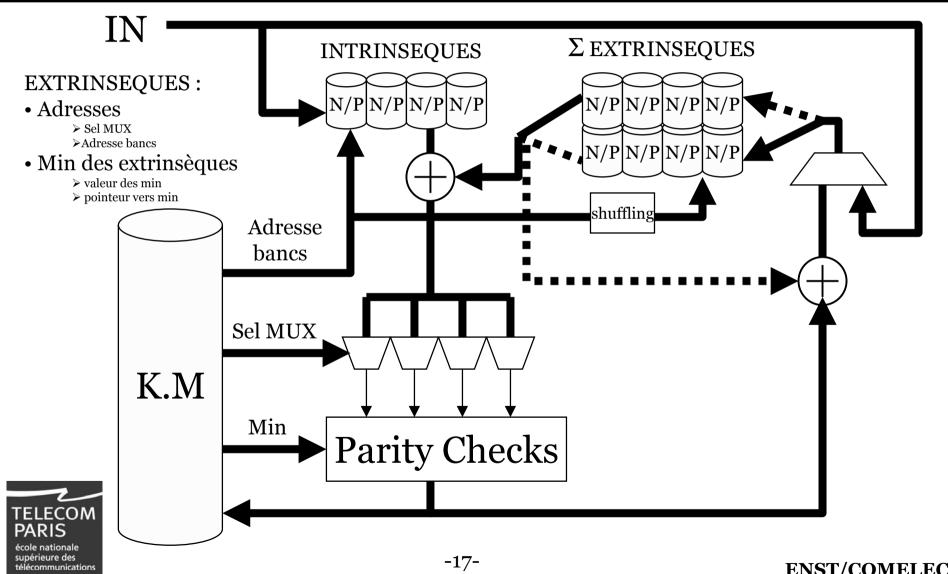

### **Architecture ENST**

- Architecture « decoder-first » => semi parallèle

- Flexibilité accrue pour tester rapidement les codes sur FPGA :

- ⇒ emploi de mémoires décrivant les Parity Checks.

- ⇒ Dégré k quelconque

- Décodage moins contraint des matrices irrégulières

- Calcul sériel des P parity checks =>performances légèrement dégradées, en partie compensées avec P élévé

- Calcul des LLR avec une méthode sous optimale

- ⇒ Utilisation de degrés élevés

- ⇒ Réduction des calculs et de la taille de la mémoire des extrinsèques

# Séquencement

### Architecture

### Performances Attendues

- Utilisation de la plateforme d'accélérération FPGA

- ⇒ 2\*XILINX XCV1000E

- □ 96 blocs mémoires 256x16 bits, 6144 CLBs

- ⇒ Téléchargement et simulation rapides de nouveaux codes

- Débit = F<sub>h</sub>.P.N/k.M.I

- ⇒ données sur 8 bits

- $\Rightarrow$  10Mbits/s avec  $F_h$ =50MHz,P=16,N=1024,M=512,k=8,I=20

## Perspectives

- Implémentation FPGA

- Étude des « error floor »

- Validation des résultats sur la quantification

- Recherche:

- ⇒ Algorithme

- ⇒ Architecture

MERCI! ©

### Calcul des LLR

-20-

Electronic Notes in Theoretical Computer Science 74 (2002)

URL: <a href="http://www.elsevier.nl/locate/entcs/volume74.html">http://www.elsevier.nl/locate/entcs/volume74.html</a>

Performance of Low Density Parity Check Codes as a Function of Actual and Assumed

Noise Levels. David J.C. MacKay and Christopher P. Hesketh