École Nationale Supérieure des Télécommunications

# Thèse

présentée pour obtenir le grade de docteur de l'École Nationale Supérieure des Télécommunications

Spécialité : Électronique et Communication

## Luis Fernando González Pérez

## Architectures VLSI pour le Codage Conjoint Source-Canal en Treillis

ENST A soutenir le 26 Octobre devant le jury composé de

Benoît MacqRapporteursBruno RouzeyreExaminateursPierre DuhamelExaminateursJorge Rogríguez Guisantes<br/>Catherine Lambert-Nebout<br/>Roger ReynaudEmmanuel BoutillonEmmanuel BoutillonDirecteur de Thèse

### École Nationale Supérieure des Télécommunications

To my family

\_\_\_\_\_

Remerciements

## Abstract

Conventionally, a digital communication system is composed of a source coder (reduction of the information to be transmitted) and a channel coder (protection against channel errors). This approach allows on the one hand to divide the transmission of information into two independent tasks, and on the other hand, to operate close to the theoretical limits for a given channel SNR. Nevertheless, this tandem system exhibits a high overall complexity and in addition, it suffers from a dramatic performance degradation when the channel conditions are poor. In this thesis, we focus on a joint source-channel trellis coding technique from both a theoretical and hardware standpoints. Our goal is to implement a simple and robust coding system for a large range of channel SNR and which could replace more efficiently the tandem system in certain applications.

The main goal of this joint source-channel trellis coding technique is to find a representation of the source sequence which minimizes the expectation of the distortion between the source sequence and the reproduction sequence decoded at the receiver end. This minimization is accomplished by a codebook design algorithm which takes into account the channel distribution during the generation of the reproduction codebook, and by the fidelity criterion employed during the quantization of the source.

In the first part of this work, we show that the type of computations required for the codebook design operation and the branch metrics of the Viterbi algorithm are quite similar. Upon proposing a simplification in the computations of the distortion measure, a reconfigurable architecture is presented which allows to implement both the codebook design algorithm and the quantization process within the same architecture.

In the next stage of this work, complexity reductions were investigated by replacing the Viterbi algorithm with a suboptimum trellis search. We showed that the M algorithm, when used in the context of joint source-channel trellis coding, presented excellent complexity-performance trade offs. Then, we focused on the design of VLSI architectures for the M algorithm, and two new ideas which are potentially more advantageous than previously reported work are proposed. The first one profits from the trellis structure to reduce up to 50% the hardware complexity of the sorting networks required by this algorithm. The second idea consists in the adaptation of the trace-back technique employed in Viterbi decoders to the M algorithm with the use of pointer tables. Finally, in the last part of this work, a joint source-channel coding technique is presented consisting in the joint optimization of the trellis quantizer described above and a convolutional code. The pairwise error probabilities required to perform the codebook design operation and the source quantization are derived from the generator polynomials of the convolutional code. Then, at the decoder end, we propose to decode the received channel sequence by means of the MAP algorithm. This algorithm provides us with the a posteriori probabilities of each trellis branch, or equivalently, with the probabilities of decoding a given codeword from the reproduction codebook. We called this a "soft" source decoding.

# **Glossary of Abbreviations**

| JSCC                 | Joint Source-Channel Coding                  |

|----------------------|----------------------------------------------|

| JSCTC                | Joint Source-Channel Trellis Coding          |

| OPTA                 | Optimum Performance Theoretically Achievable |

| $\mathrm{TQ}$        | Trellis Quantization                         |

| VQ                   | Vector Quantization                          |

| LBG                  | Linde-Buzo-Gray                              |

| MAP                  | Maximum A Posteriori                         |

| APP                  | A Posteriori Probabilities                   |

| BCJR                 | Bahl-Cocke-Jelinek-Raviv                     |

| VA                   | Viterbi Algorithm                            |

| VA                   | M Algorithm                                  |

| MA                   | M Algorithm                                  |

| $\mathrm{TCQ}$       | Trellis Coded Quantization                   |

| TCM                  | Trellis Coded Modulation                     |

| CELP                 | Code Excited Linear Prediction               |

|                      |                                              |

| MSE                  | Mean Square Error                            |

| SNR                  | channel Signal to Noise Ratio                |

| $\operatorname{SQR}$ | Signal to Quantization noise Ratio           |

| BSC                  | Binary Symmetric Channel                     |

| AWGN                 | Additive White Gaussian Noise                |

| BPSK                 | Binary Phase Shift Keying                    |

| $\mathbf{FSM}$       | Finite State Machine                         |

| LUT                  | Look-Up Table                                |

| $\operatorname{CL}$  | Computational Load                           |

| MSB                  | Most Significant Bit                         |

| LSB                  | Least Significant Bit                        |

|                      |                                              |

- RE Register Exchange

- TB Trace-Back

- PM Path Metric

- BM Branch Metric

- ${\rm ACS} \qquad {\rm Add}\text{-}{\rm Compare-Select}$

- BMU Branch Metric Unit

- SMU Survivor Memory Unit

- LIFO Last In First Out

- FIFO First In First Out

- VLSI Very Large Scale Integration

- FPGA Field Programmable Gate Array

- DSP Digital Signal Processor

- TTL Transistor Transistor Logic

- CER Comparison-Exchange-Rejection

- MRO Merging Rejection Operator

# **Glossary of Symbols**

| time index                                |

|-------------------------------------------|

| trellis constraint length                 |

| source alphabet                           |

| source sequence                           |

| source symbols                            |

| reproduction codebook                     |

| reproduction sequence                     |

| reproduction codeword                     |

| decoded source sequence                   |

| decoded source symbol                     |

| binary label associated to codeword $y_i$ |

| binary sequence                           |

| binary symbol                             |

| transmitted channel sequence              |

| transmitted channel symbol                |

| received channel sequence                 |

| received channel symbol                   |

| probability density function              |

| source code rate                          |

| channel code rate                         |

| channel capacity                          |

| bandwidth                                 |

| average signal power                      |

| noise spectral density                    |

| channel transition error probability      |

| rate-distortion function                  |

| OPTA function                             |

| mutual information                        |

| distortion                                |

|                                           |

| d(x,y)        | per-letter distortion measure                                             |

|---------------|---------------------------------------------------------------------------|

| d(i,j)        | hamming distance                                                          |

| Q(x)          | quantization function                                                     |

| $Q(x)^{-1}$   | decoding function                                                         |

| $Q_i$         | set of source symbols (vectors) coded by $y_i$                            |

| $  Q_i  $     | cardinality of $Q_i$                                                      |

| $\sigma^2$    | variance                                                                  |

| w             | additive white gaussian noise variable                                    |

| $Pr(y_i y_j)$ | probability of decoding codeword $y_j$ given that codeword $y_i$ was sent |

| $L_{TS}$      | length of the training sequence                                           |

| L             | decoding depth in trellis search algorithms                               |

| $S_i$         | ith trellis state                                                         |

| M             | number of surviving paths in a trellis search algorithm                   |

## Contents

| R  | emer                  | ciemen   | ts                                                                                                           | iii          |

|----|-----------------------|----------|--------------------------------------------------------------------------------------------------------------|--------------|

| A  | bstra                 | nct      |                                                                                                              | $\mathbf{v}$ |

| G  | lossa                 | ry of A  | bbreviations                                                                                                 | vii          |

| G  | lossa                 | ry of S  | ymbols                                                                                                       | ix           |

| In | trod                  | uction   |                                                                                                              | 1            |

|    | $\operatorname{Diss}$ | ertation | $\mathbf{Outline}$                                                                                           | 3            |

|    | Pub                   | lished V | Vork                                                                                                         | 4            |

| 1  | Joir                  | nt Sour  | ce-Channel Coding: Fundamentals and State of the Art                                                         | <b>5</b>     |

|    | 1.1                   | Digita   | Communication System                                                                                         | 5            |

|    | 1.2                   | Source   | Coding                                                                                                       | 6            |

|    |                       | 1.2.1    | Distortion Measures                                                                                          | 7            |

|    |                       | 1.2.2    | Rate-Distortion Function                                                                                     | 9            |

|    |                       | 1.2.3    | Scalar Quantization                                                                                          | 10           |

|    |                       | 1.2.4    | Vector Quantization                                                                                          | 12           |

|    | 1.3                   | Chann    | el Coding                                                                                                    | 15           |

|    |                       | 1.3.1    | Channel Models                                                                                               | 15           |

|    |                       | 1.3.2    | Channel Capacity                                                                                             | 17           |

|    | 1.4                   | Joint S  | Source-Channel Coding                                                                                        | 19           |

|    | 1.5                   | State of | of the Art on JSCC $\ldots$ | 21           |

|    |                       | 1.5.1    | Concatenated joint source-channel coders                                                                     | 21           |

|    |                       | 1.5.2    | Joint source-channel decoders                                                                                | 22           |

|    |                       | 1.5.3    | Robust source coders                                                                                         | 23           |

|          |                                         | 1.5.4                               | Joint optimization of source and channel coders                                                            | 24      |  |  |

|----------|-----------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------|---------|--|--|

| <b>2</b> | Joir                                    | nt Soui                             | rce-Channel Trellis Coding                                                                                 | 27      |  |  |

|          | 2.1                                     | Trellis                             | Source Coding                                                                                              | 28      |  |  |

|          |                                         | 2.1.1                               | Codebook Desing                                                                                            | 32      |  |  |

|          |                                         | 2.1.2                               | Codebook Initialization                                                                                    | 32      |  |  |

|          | 2.2                                     | Joint                               | Source-Channel Trellis Coding                                                                              | 34      |  |  |

|          |                                         | 2.2.1                               | Codebook Design and Initialization                                                                         | 37      |  |  |

|          |                                         | 2.2.2                               | Performances                                                                                               | 38      |  |  |

|          | 2.3                                     | Conclu                              | usion                                                                                                      | 43      |  |  |

| 3        | Joir                                    | nt Soui                             | rce-Channel Trellis Coding Architecture                                                                    | 45      |  |  |

|          | 3.1                                     |                                     | ecture for Codebook Design                                                                                 | 46      |  |  |

|          |                                         | 3.1.1                               | Architecture for Method 1                                                                                  | 48      |  |  |

|          |                                         | 3.1.2                               | Architecture for Method 2                                                                                  | 50      |  |  |

|          |                                         | 3.1.3                               | Codeword Label Decoder                                                                                     | 52      |  |  |

|          |                                         | 3.1.4                               | Channel Transition Probability                                                                             | 52      |  |  |

|          | 3.2                                     | Hardw                               | vare Implementation of the Distortion Measure $\ldots \ldots \ldots \ldots \ldots$                         | 53      |  |  |

|          |                                         | 3.2.1                               | Global Architecture for Method 1                                                                           | 55      |  |  |

|          |                                         | 3.2.2                               | Global Architecture for Method 2                                                                           | 57      |  |  |

|          | 3.3 Measures for Increasing Performance |                                     |                                                                                                            |         |  |  |

|          |                                         | 3.3.1                               | Parallelization of Method 1                                                                                | 60      |  |  |

|          |                                         | 3.3.2                               | Parallelization of Method 2                                                                                | 63      |  |  |

|          |                                         | 3.3.3                               | Architecture Comparison                                                                                    | 63      |  |  |

|          | 3.4                                     | Adapt                               | ability to the Extension Algorithm                                                                         | 65      |  |  |

|          |                                         | 3.4.1                               | Shift Registers and Counters                                                                               | 65      |  |  |

|          |                                         | 3.4.2                               | Channel Transition Probability                                                                             | 66      |  |  |

|          |                                         | 3.4.3                               | Codebook Memory                                                                                            | 68      |  |  |

|          | 3.5                                     | Conclu                              | usion $\ldots$            | 68      |  |  |

| 4        |                                         | dy of<br>llis Co                    | a Suboptimum VLSI Architecture for Joint Source-Channe<br>ding                                             | l<br>71 |  |  |

|          | 4.1                                     | Archit                              | ectural Issues of the Viterbi Algorithm                                                                    | 72      |  |  |

|          |                                         | 4.1.1                               | The Viterbi Algorithm                                                                                      | 72      |  |  |

|          |                                         | 4.1.2                               | The Add-Compare-Select Unit                                                                                |         |  |  |

| 4        | Stu<br>Tre                              | dy of<br>llis Co<br>Archit<br>4.1.1 | a Suboptimum VLSI Architecture for Joint Source-Channe<br>ding<br>sectural Issues of the Viterbi Algorithm | •       |  |  |

|          |     | 4.1.3   | Survivor Memory Management                                                                                                     |

|----------|-----|---------|--------------------------------------------------------------------------------------------------------------------------------|

|          |     |         | 4.1.3.1 Register Exchange Algorithm                                                                                            |

|          |     |         | 4.1.3.2 Trace-Back Algorithm                                                                                                   |

|          | 4.2 | Quest   | for a Suboptimum Trellis Search Algorithm                                                                                      |

|          | 4.3 | Classif | fication of the Trellis Search Algorithms                                                                                      |

|          |     | 4.3.1   | Metric-first example: The Stack Algorithm                                                                                      |

|          |     | 4.3.2   | Depth-first example: The Fano Algorithm                                                                                        |

|          |     | 4.3.3   | Breadth-first example: The M algorithm                                                                                         |

|          |     | 4.3.4   | Algorithm Selection                                                                                                            |

|          | 4.4 | JSCT    | C with the M Algorithm                                                                                                         |

|          |     | 4.4.1   | Computational Load Comparison with the VA                                                                                      |

|          |     | 4.4.2   | Peformance Comparison with the VA                                                                                              |

|          | 4.5 | Conclu  | 1sions                                                                                                                         |

| <b>5</b> | VLS | SI Arcl | nitectures for the M Algorithm 99                                                                                              |

|          | 5.1 | The M   | $[Algorithm revisited \ldots 100]$  |

|          | 5.2 | The Se  | $\operatorname{prting}$ Architecture                                                                                           |

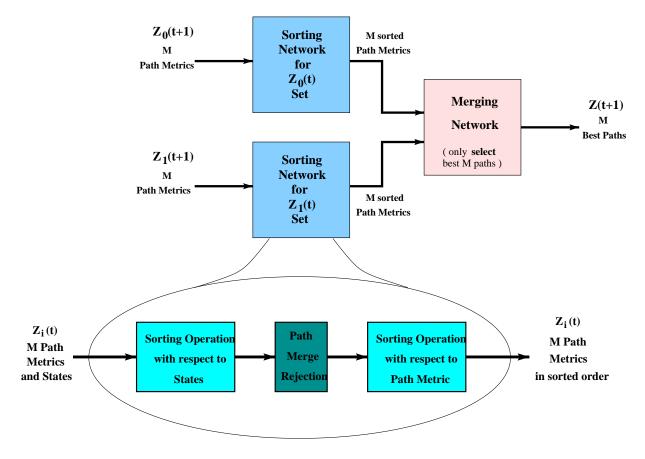

|          |     | 5.2.1   | Introduction of Path Merge Rejection within the Sorting Circuit $106$                                                          |

|          |     | 5.2.2   | State of the Art in Sorting Architectures for the M Algorithm 110                                                              |

|          |     | 5.2.3   | First Method for Selecting the Best Paths: Path Merge Detectors . 111                                                          |

|          |     | 5.2.4   | Second Method for Selecting the Best Paths: Combined Sorting and Selection                                                     |

|          |     | 5.2.5   | Third Method for Selecting the Best Paths: Delayed State Label<br>Sorting                                                      |

|          |     | 5.2.6   | $Conclusion \dots \dots$ |

|          | 5.3 | Surviv  | or Memory Management                                                                                                           |

|          |     | 5.3.1   | Conventional Approach of Survivor Memory Management in the M<br>Algorithm                                                      |

|          |     | 5.3.2   | Trace-Back Techniques Adapted to the M Algorithm                                                                               |

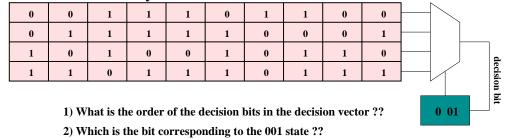

|          |     |         | 5.3.2.1 Trace-Back Technique by Comparison of Visited States 131                                                               |

|          |     |         | 5.3.2.2 Trace-Back Technique with Path-Number Pointer 132                                                                      |

|          |     | 5.3.3   | Improving Hardware Efficiency: Hybrid Architectures                                                                            |

|          |     |         | 5.3.3.1 Block Trace-Back for the M Algorithm                                                                                   |

|          |     |         | 5.3.3.2 Forward Trace-Back for the M algorithm                                                                                 |

|    | 5.4   | Hardware Comparison with the V                              | iterbi Algorithm                           |

|----|-------|-------------------------------------------------------------|--------------------------------------------|

|    | 5.5   | Hardware Realization of the M A                             | gorithm                                    |

|    |       | 5.5.1 Sorting Architecture                                  |                                            |

|    |       | 5.5.2 Survivor Memory Manage                                | ments Architecture                         |

|    |       | 5.5.3 Logic Synthesis Results .                             |                                            |

|    | 5.6   | $Conclusion \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $         |                                            |

| 6  |       | nt Optimization of a Trellis Sour<br>h Soft Source Decoding | ce and Convolutional Channel Coders<br>145 |

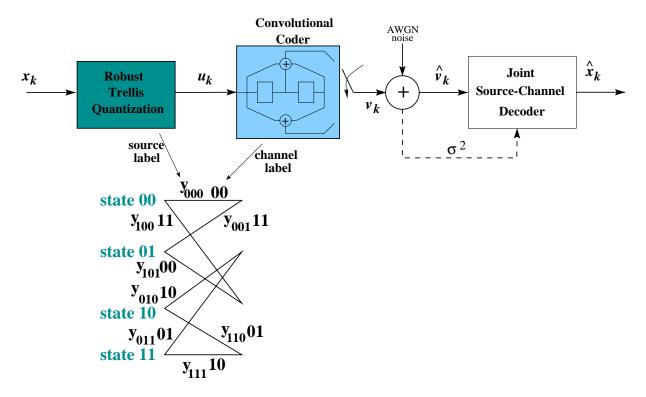

|    | 6.1   | 0                                                           |                                            |

|    | 6.2   |                                                             |                                            |

|    | 6.3   |                                                             |                                            |

|    |       |                                                             | e Pairwise Error Probability 149           |

|    |       |                                                             | $u_i(d)$ from the Transfer Function a the  |

|    | 6.4   | Codebook Design                                             |                                            |

|    | 6.5   | The BCJR Algorithm as Soft Sou                              | rce Decoder                                |

|    | 6.6   | Simulation Results                                          |                                            |

|    | 6.7   | $Conclusion \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $         |                                            |

| Co | onclu | ision and Future Work                                       | 163                                        |

|    | Cone  | clusion                                                     |                                            |

|    | Futu  | ıre Work                                                    |                                            |

| Α  |       | ce-Back Techniques in Survivor<br>orithm                    | Memory Management for the Viterbi<br>167   |

|    | A.1   | l-Pointer Trace-Back                                        |                                            |

|    | A.2   | Improving Hardware Efficiency: H                            | ybrid Survivor Memory Management Ar-       |

|    |       | A.2.1 Block Trace-Back                                      |                                            |

|    |       | A.2.2 Register-Exchange-Pointer                             | Trace-Back                                 |

|    | A.3   |                                                             | nt Survivor Memory Management Tech-        |

| в  | A B   | Brief Survey on Sorting Algorit                             | hms 179                                    |

|    | B.1   | Parallel Sorting                                            |                                            |

|    |       | B.1.1 Batcher's Odd-Even Sortin                             | ng Network                                 |

| Bibliog | raphy  | 1:                                                                | 93 |

|---------|--------|-------------------------------------------------------------------|----|

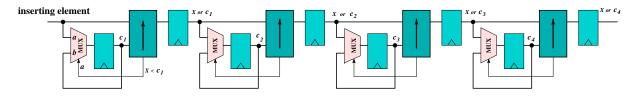

|         | B.2.3  | Parallel Insertion                                                | 90 |

|         | B.2.2  | Dichotomic Insertion                                              | 88 |

|         | B.2.1  | Single Insertion                                                  | 87 |

| B.2     | Serial | Sorting $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$ | 87 |

|         | B.1.3  | Bubble Sort                                                       | 87 |

|         | B.1.2  | Batcher's Bitonic Sorting Network                                 | 84 |

# List of Figures

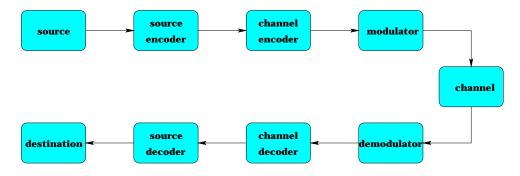

| 1.1                                                                                                                | Conventional communication system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                                                                              |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

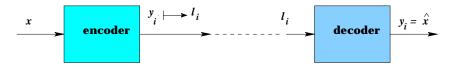

| 1.2                                                                                                                | Source coder-decoder pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7                                                                                              |

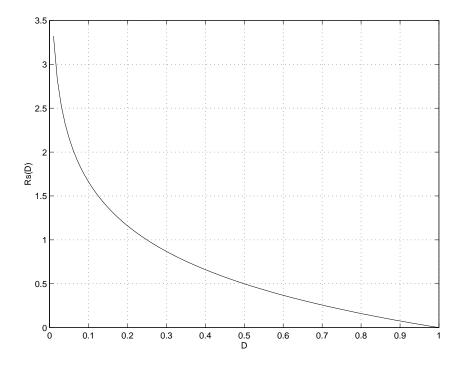

| 1.3                                                                                                                | Rate-distortion function of a gaussian source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10                                                                                             |

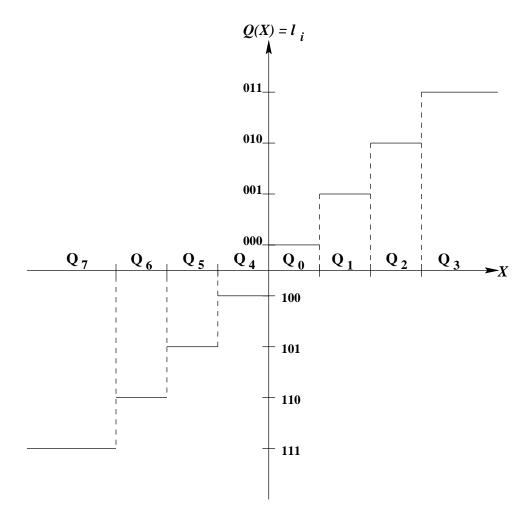

| 1.4                                                                                                                | Scalar quantizer with 8 reproduction levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11                                                                                             |

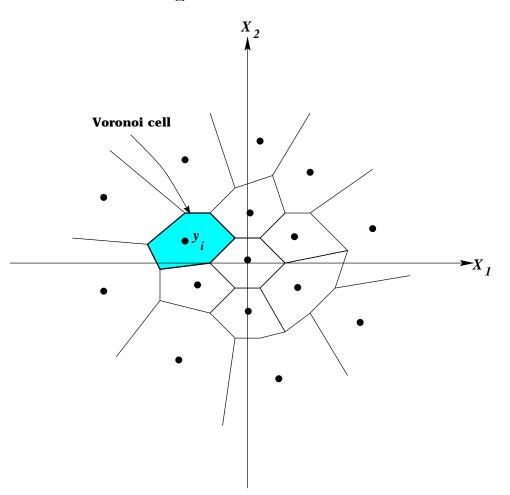

| 1.5                                                                                                                | Bidimensional Vector Quantizer with 16 reproduction vectors. $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13                                                                                             |

| 1.6                                                                                                                | $Channel \ coder-decoder \ pair. \ . \ . \ . \ . \ . \ . \ . \ . \ . \$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15                                                                                             |

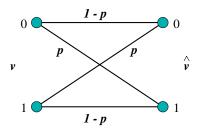

| 1.7                                                                                                                | Binary Symmetric Channel Model.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16                                                                                             |

| 1.8                                                                                                                | Additive White Gaussian Noise channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16                                                                                             |

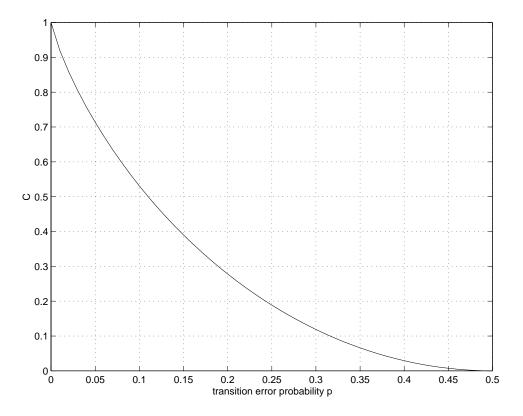

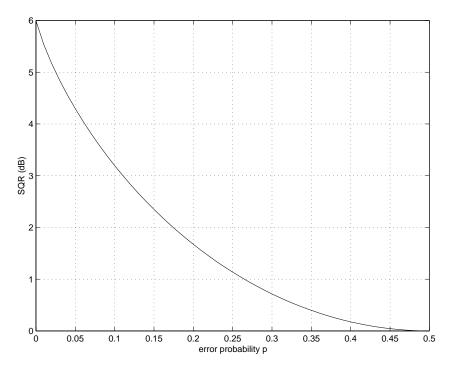

| 1.9                                                                                                                | Channel Capacity of a BSC channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18                                                                                             |

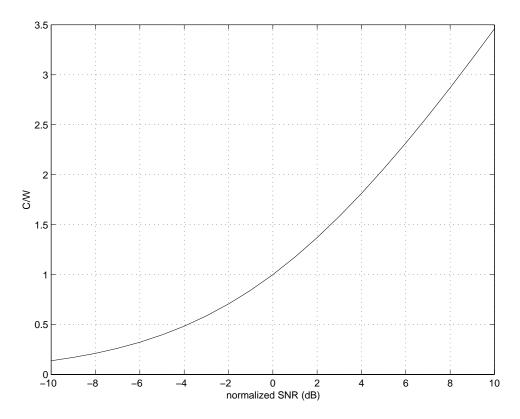

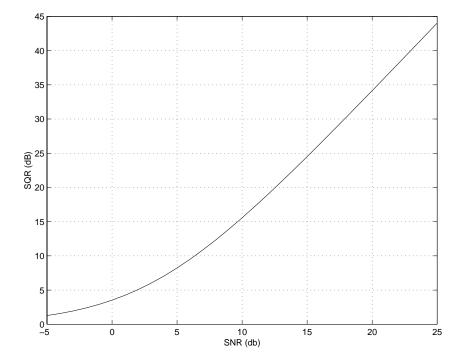

| 1.10                                                                                                               | Channel Capacity of an AWGN channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18                                                                                             |

| 1.11                                                                                                               | OPTA curve for gaussian source and BSC channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20                                                                                             |

| 1 1 2                                                                                                              | OPTA curve for gaussian source and AWGN channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20                                                                                             |

| 1.14                                                                                                               | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                |

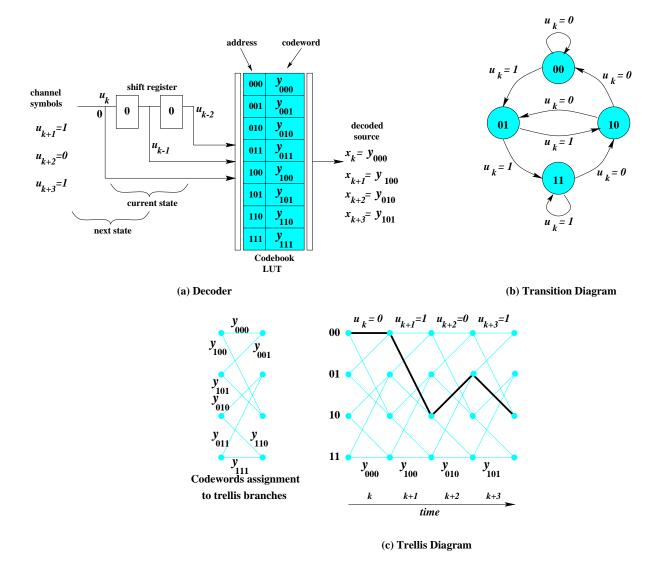

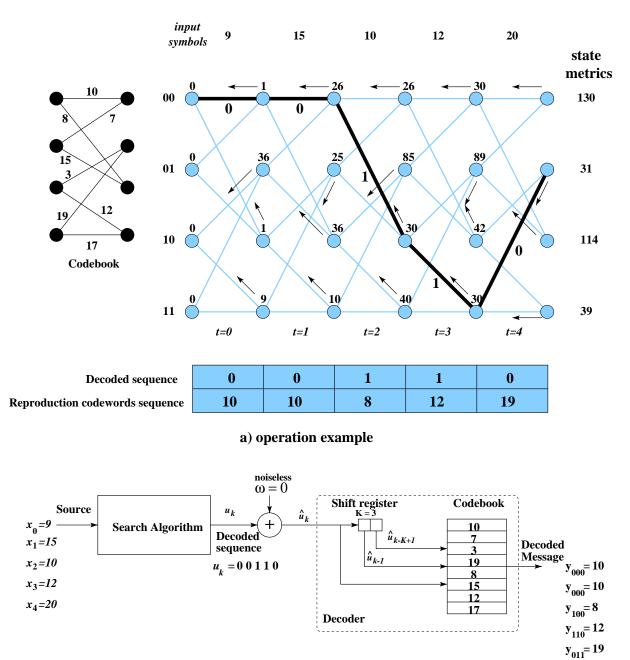

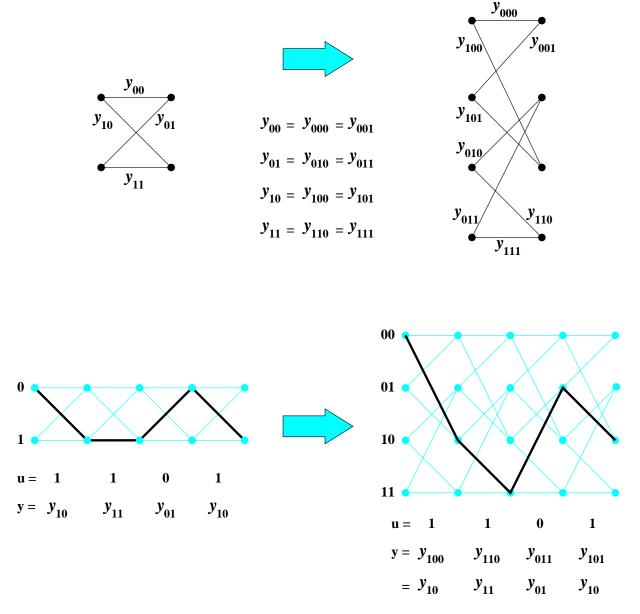

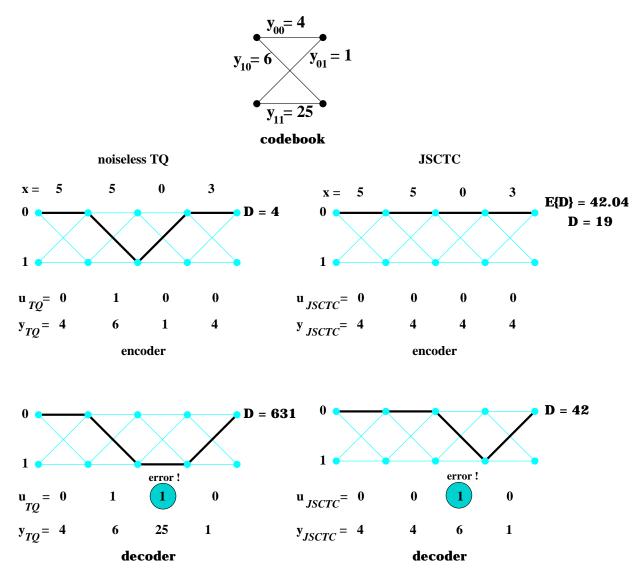

| 2.1                                                                                                                | Trellis quantizer decoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29                                                                                             |

|                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $\frac{29}{31}$                                                                                |

| 2.1                                                                                                                | Trellis quantizer decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                |

| 2.1<br>2.2                                                                                                         | Trellis quantizer decoder.       Trellis quantizer structure and operation example.         Trellis quantizer structure and operation example.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31                                                                                             |

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> </ol>                                                                  | Trellis quantizer decoder.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 31<br>33                                                                                       |

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> </ol>                                                     | Trellis quantizer decoder.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 31<br>33<br>36                                                                                 |

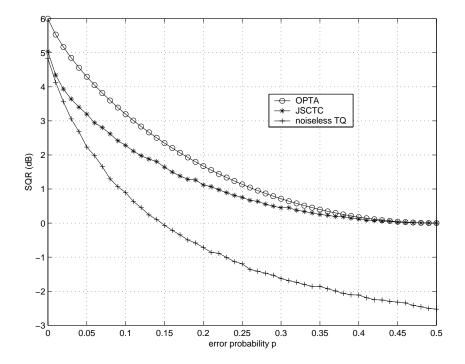

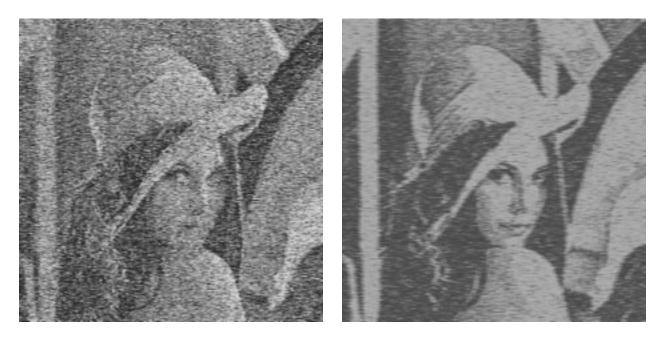

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> </ol>                                        | Trellis quantizer decoderTrellis quantizer structure and operation exampleCodeword assignment in the Extension algorithmJSCTC vs Noiseless Trellis QuantizationJSCTC vs TQ Performance for BSC and gaussian source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31<br>33<br>36<br>38                                                                           |

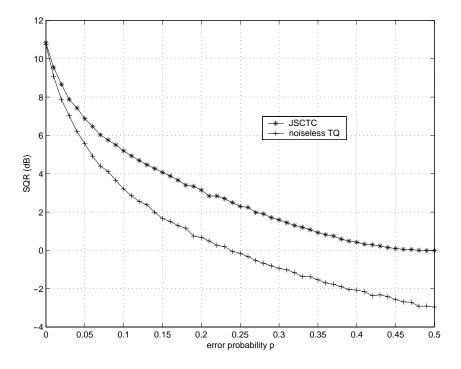

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> </ol>                           | Trellis quantizer decoder.       .         Trellis quantizer structure and operation example.       .         Codeword assignment in the Extension algorithm.       .         JSCTC vs Noiseless Trellis Quantization.       .         JSCTC vs TQ Performance for BSC and gaussian source.       .         JSCTC vs TQ Performance for BSC and markov source.       .         JSCTC vs tandem system performance for AWGN channel and gaussian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 31<br>33<br>36<br>38<br>39                                                                     |

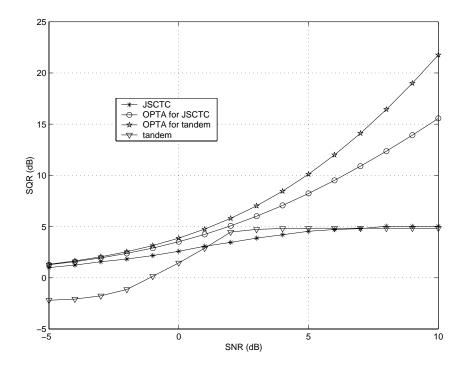

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> </ol>              | Trellis quantizer decoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>31</li> <li>33</li> <li>36</li> <li>38</li> <li>39</li> <li>40</li> </ul>             |

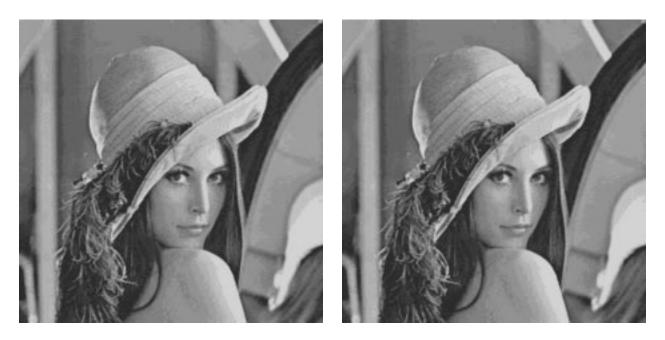

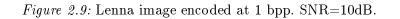

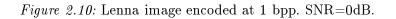

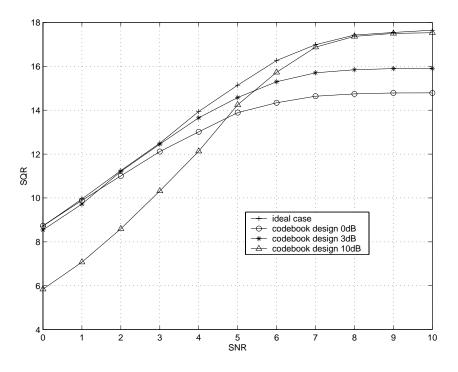

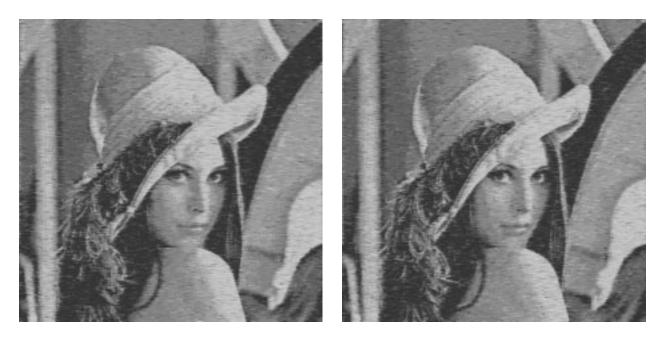

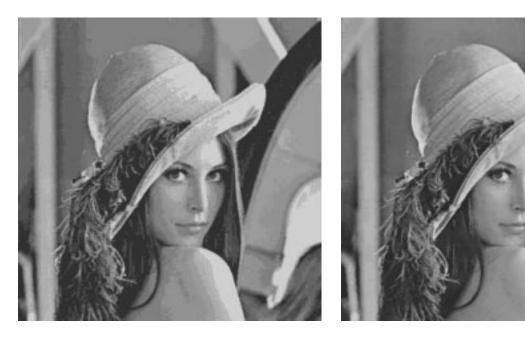

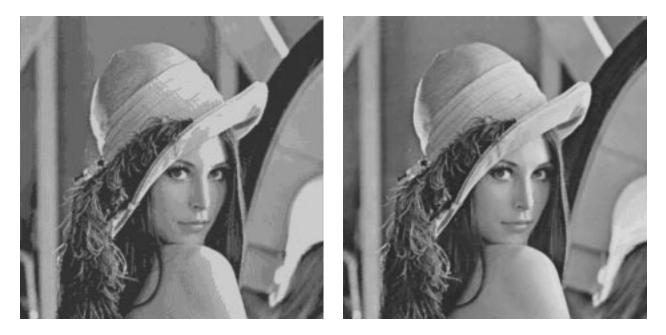

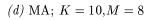

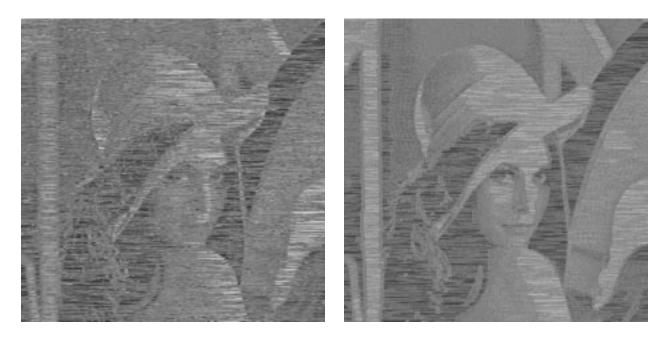

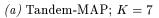

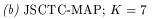

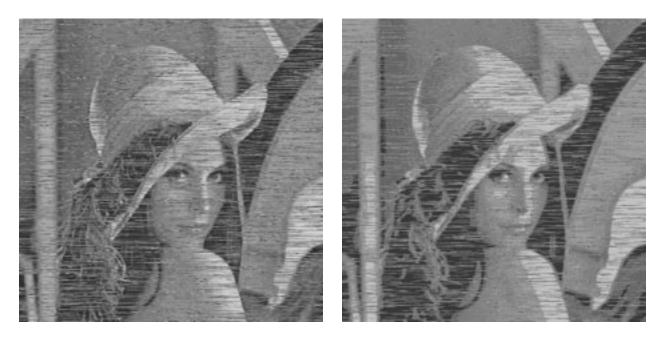

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> </ol> | Trellis quantizer decoder.Trellis quantizer structure and operation example.Codeword assignment in the Extension algorithm.JSCTC vs Noiseless Trellis Quantization.JSCTC vs TQ Performance for BSC and gaussian source.JSCTC vs TQ Performance for BSC and markov source.JSCTC vs tandem system performance for AWGN channel and gaussian source.Original Lenna image 8 bpp.Lenna image encoded at 1 bpp. SNR=10dB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>31</li> <li>33</li> <li>36</li> <li>38</li> <li>39</li> <li>40</li> <li>41</li> </ul> |

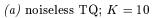

| 2.12 | Pixel range of the image decoded with the noiseless TQ and JSCTC                                            | 43 |

|------|-------------------------------------------------------------------------------------------------------------|----|

| 3.1  | Pseudo-programs describing to ways of implementing the codebook design algorithm.                           | 47 |

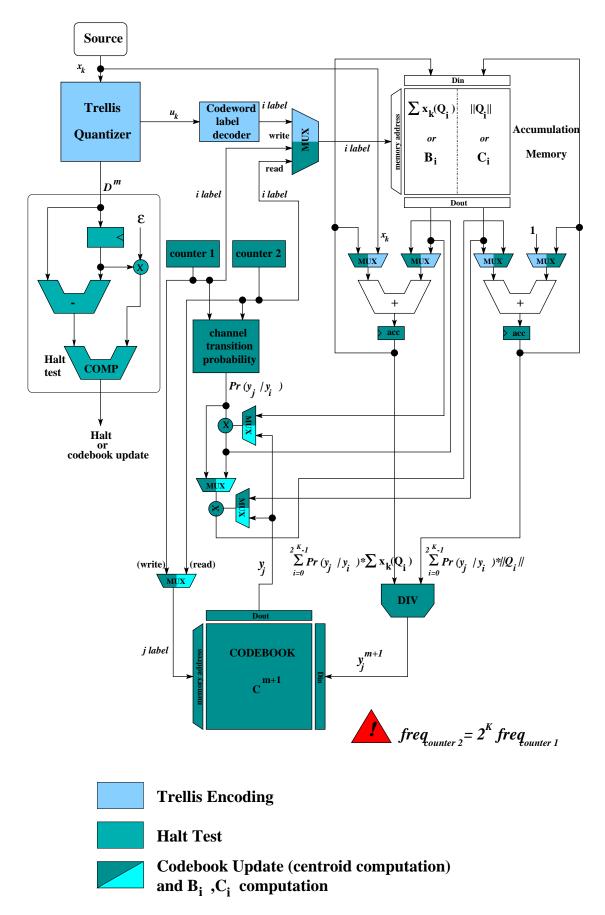

| 3.2  | Hardware architecture for the first method of codebook design                                               | 49 |

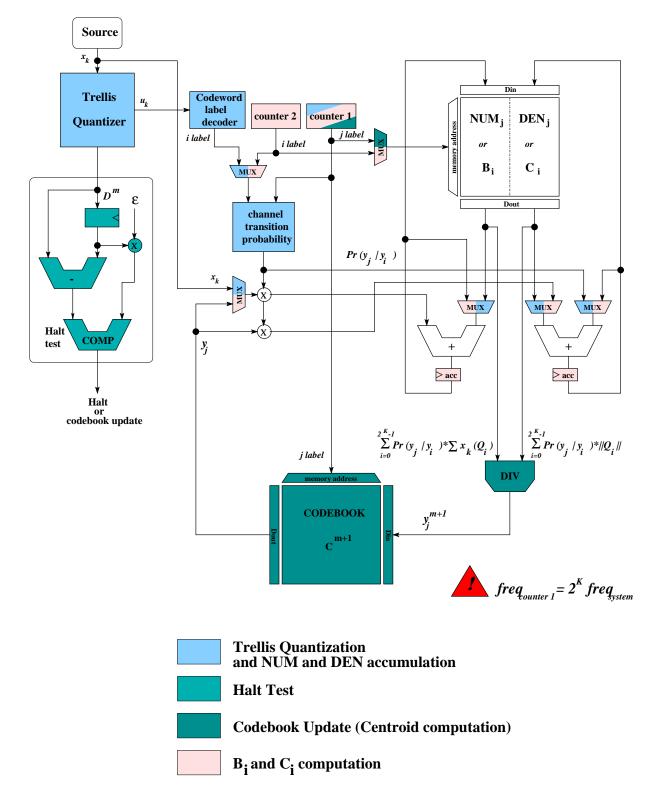

| 3.3  | Hardware architecture for the second method of codebook design.                                             | 51 |

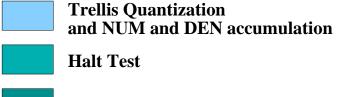

| 3.4  | Codeword Label Decoder.                                                                                     | 52 |

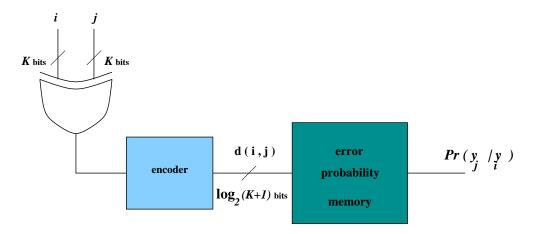

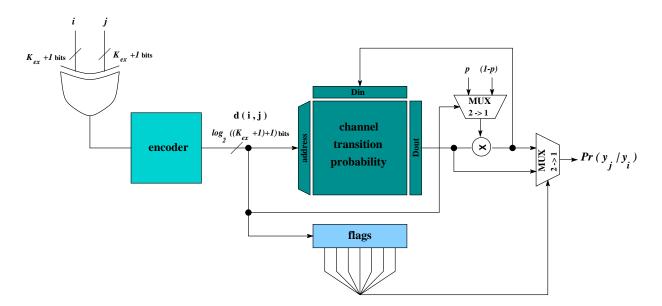

| 3.5  | Channel Transition Probability Block.                                                                       | 53 |

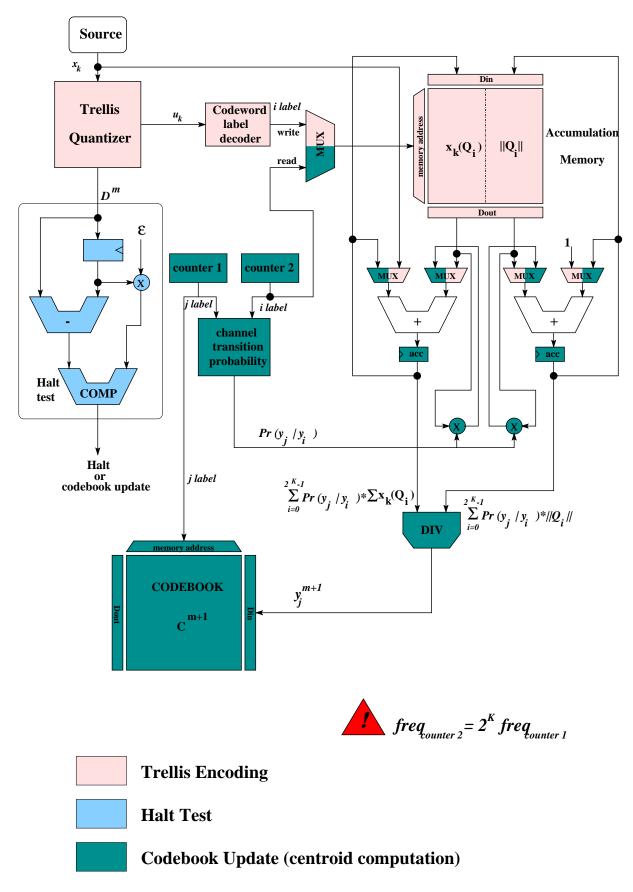

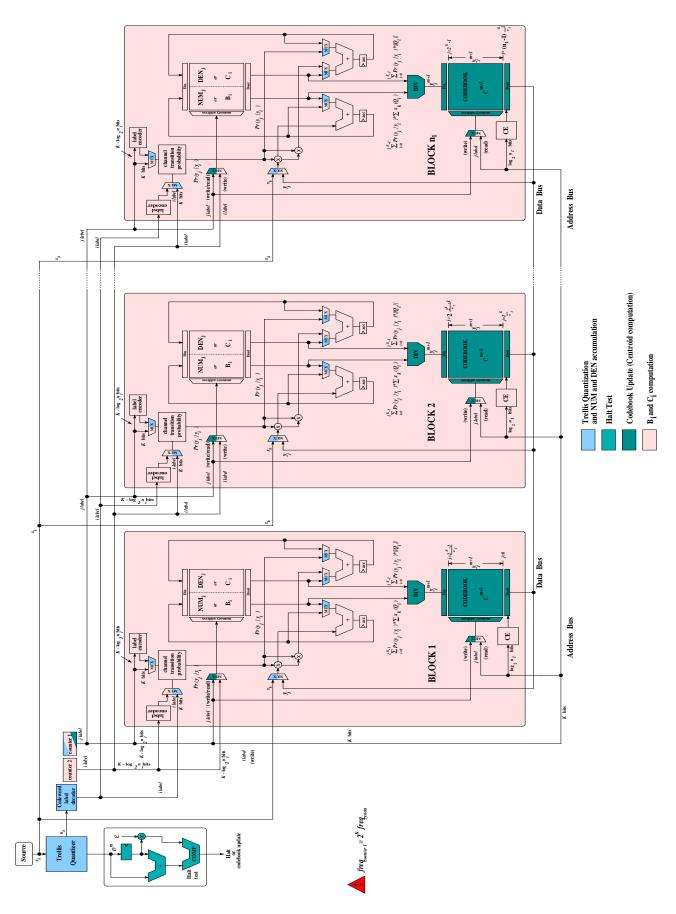

| 3.6  | Global architecture for method 1                                                                            | 56 |

| 3.7  | Global architecture for method 2                                                                            | 58 |

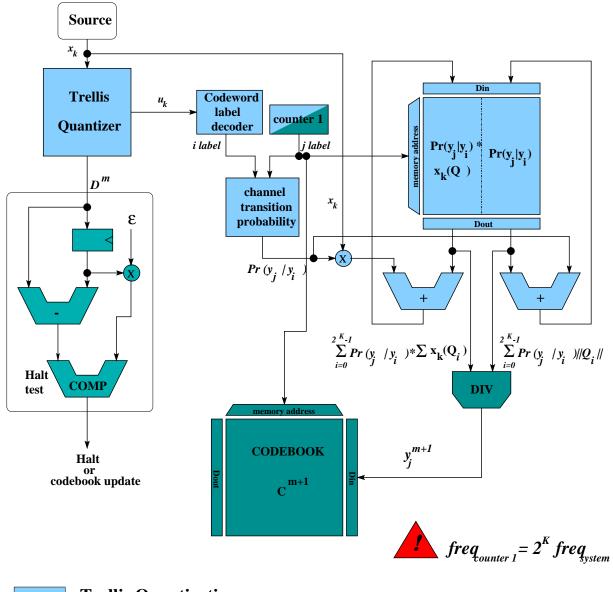

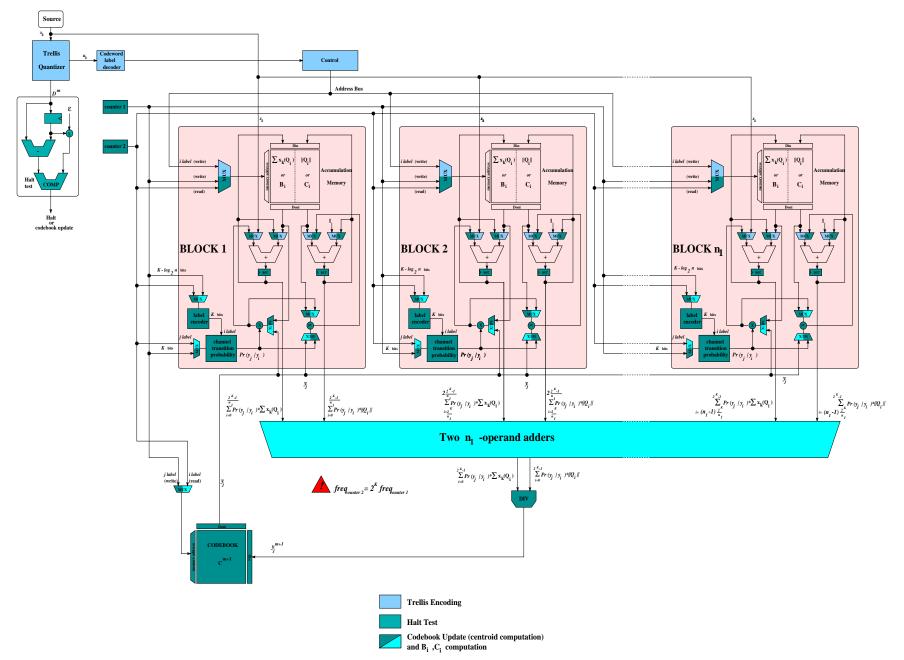

| 3.8  | Parallel architecture of method 1                                                                           | 61 |

| 3.9  | Parallel architecture of method 2                                                                           | 64 |

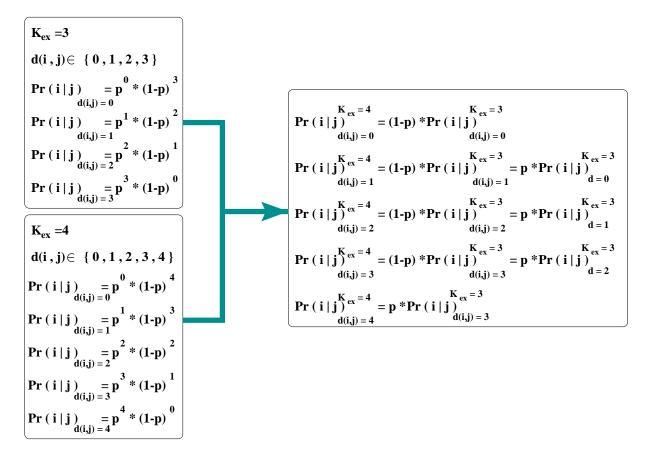

| 3.10 | Channel transition probability dependency between successive constraint lengths in the extension algorithm. | 67 |

| 3.11 | Architecture for updating the channel transition probability memory. $\ldots$                               | 67 |

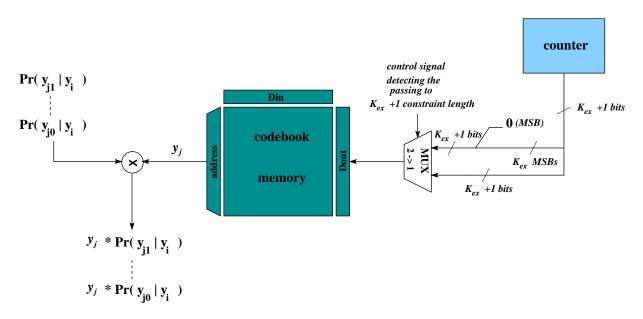

| 3.12 | Architecture for codebook duplication in the extension algorithm. $\ldots$ .                                | 68 |

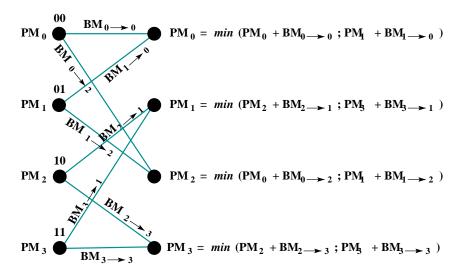

| 4.1  | Path metric updating in the Viterbi algorithm                                                               | 73 |

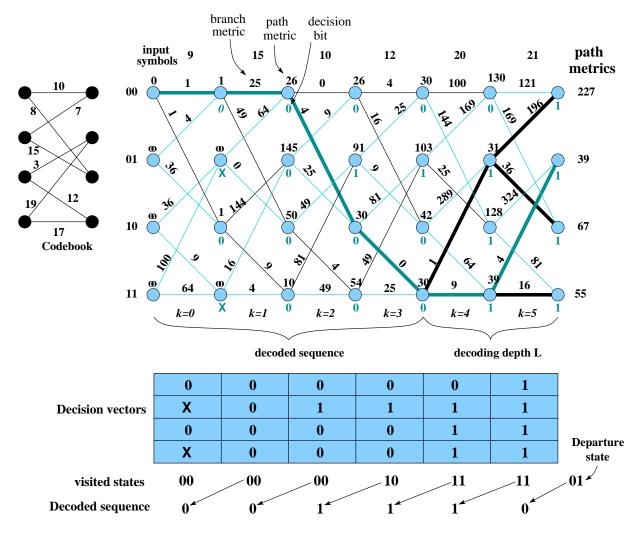

| 4.2  | Operation example of the Viterbi algorithm.                                                                 | 75 |

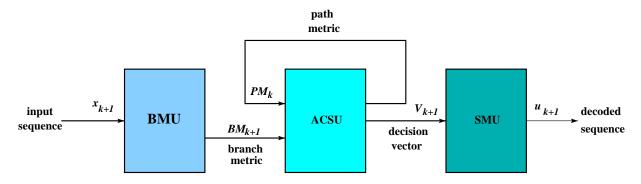

| 4.3  | Block diagram of the Viterbi decoder                                                                        | 76 |

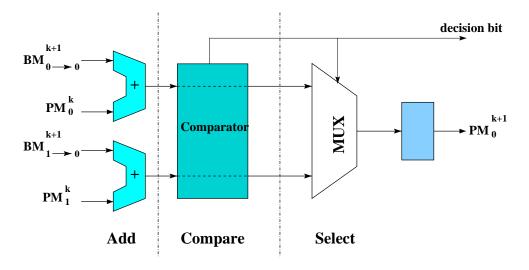

| 4.4  | Basic processing element of the ACS operation.                                                              | 77 |

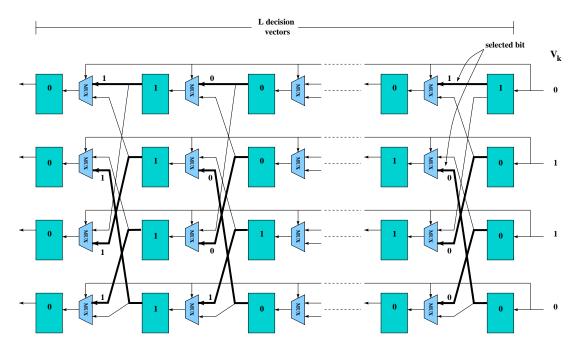

| 4.5  | Register Exchange architecture.                                                                             | 78 |

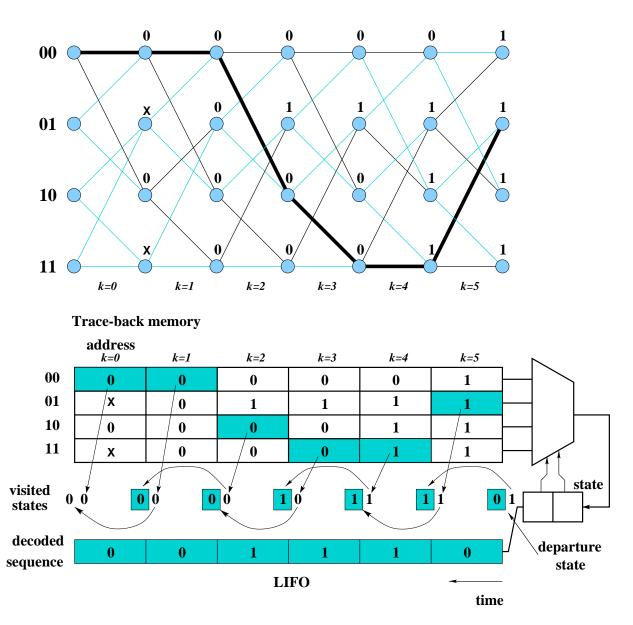

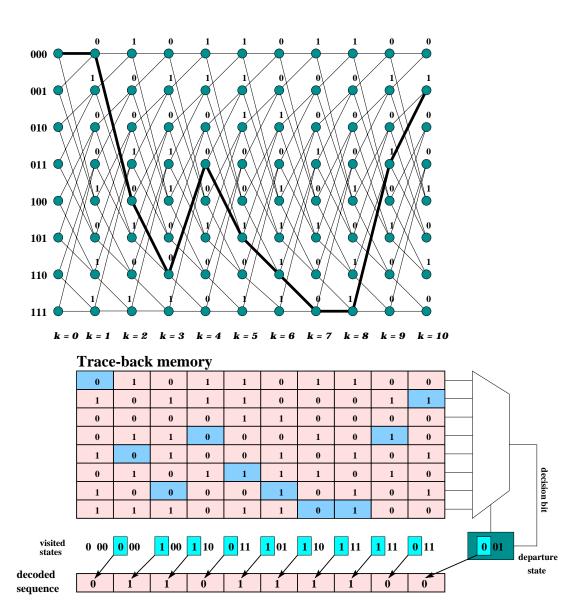

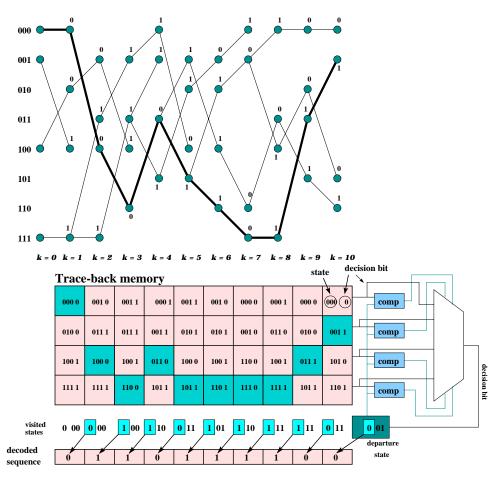

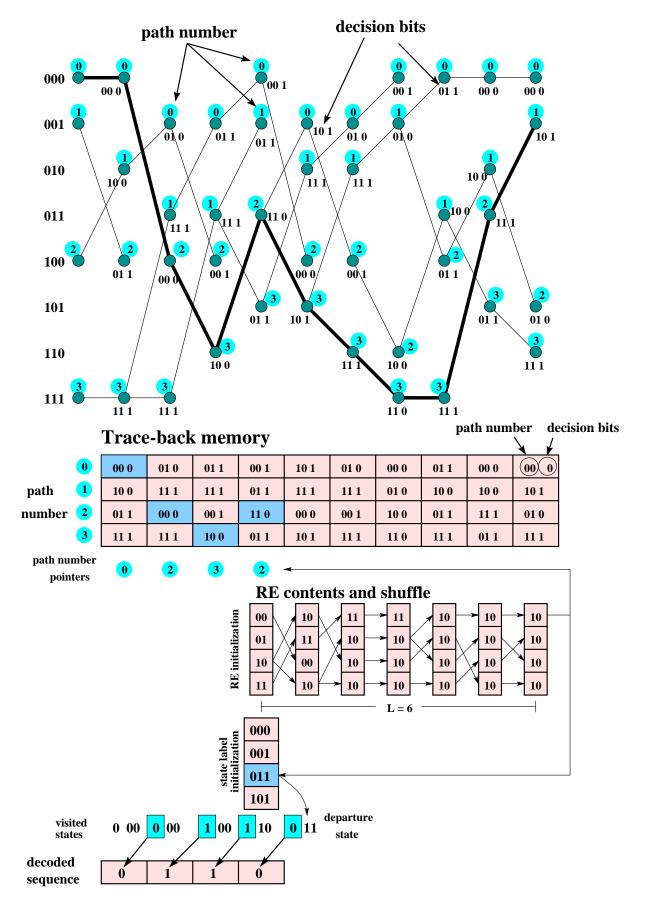

| 4.6  | Operation Example of the Trace-Back Algorithm.                                                              | 80 |

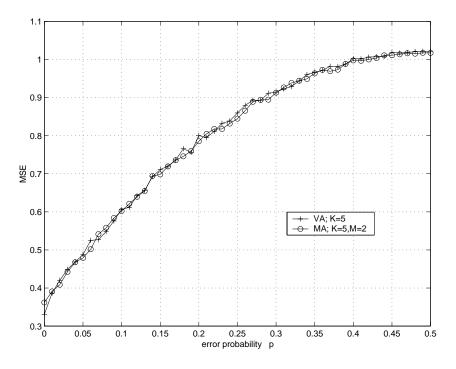

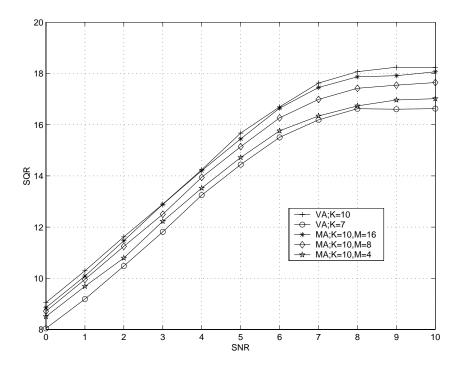

| 4.7  | Suboptimum robust trellis quantizer performance on gaussian sources                                         | 88 |

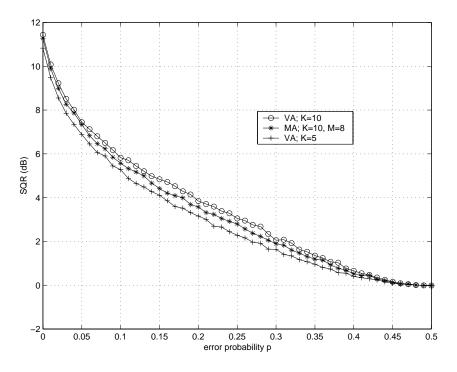

| 4.8  | Suboptimum robust trellis quantizer performance on first-order gauss-markov sources.                        | 89 |

| 4.9  | SQR vs SNR performance of the Viterbi and M algorithm for the transmission of the Lenna image.              | 90 |

| 4.10 | SQR vs SNr performance of the Viterbi and M algorithm with the same hardware complexity.                    | 91 |

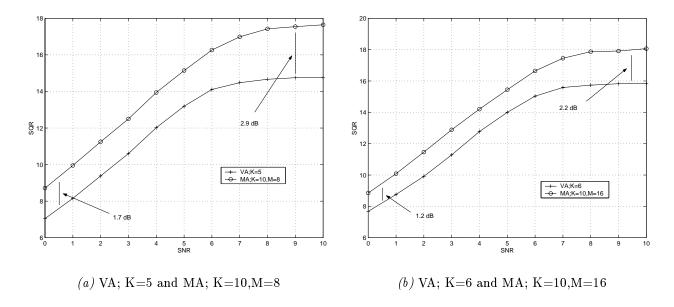

| 4.11 | Effects of channel mismatch in suboptimum trellis quantization.                                             | 92 |

| 4.12 | Overall performance with reduced computational load at SNR=10 dB $\ldots$ .                                 | 93 |

| 4.13 | Overall performance with reduced computational load at SNR=0 dB $\ .$                                       | 94 |

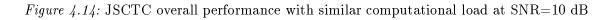

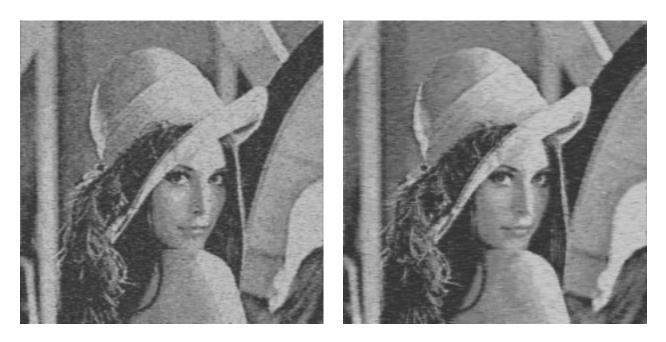

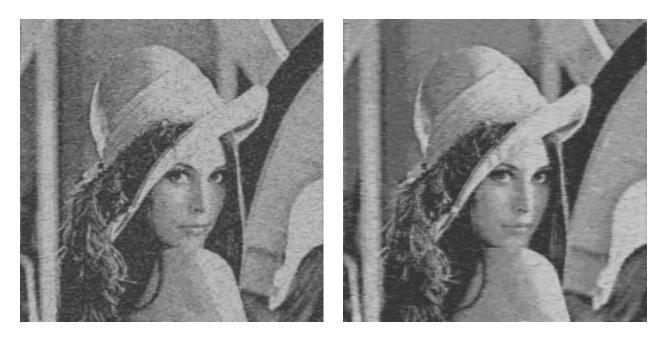

| 4.14 | JSCTC overall performance with similar computational load at SNR=10 dB $$                                   | 95 |

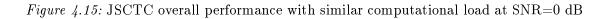

| 4.15 | JSCTC overall performance with similar computational load at SNR=0 dB $$                                    | 96 |

|      |                                                                                                             |    |

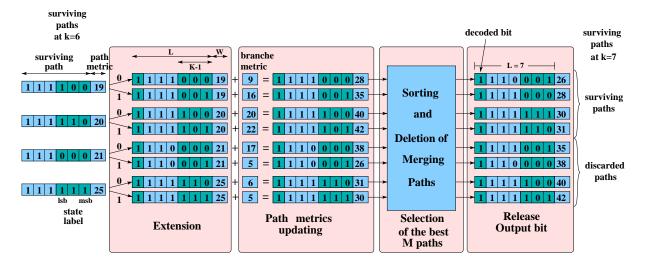

| 5.1  | Operation example of the M algorithm.                                                                                                      | 102 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

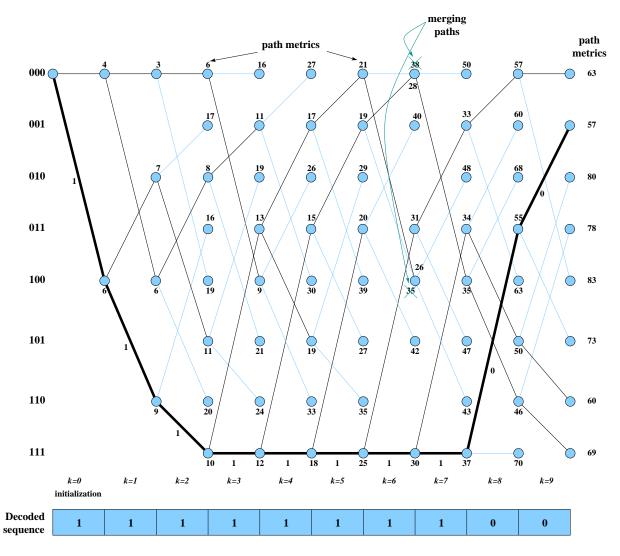

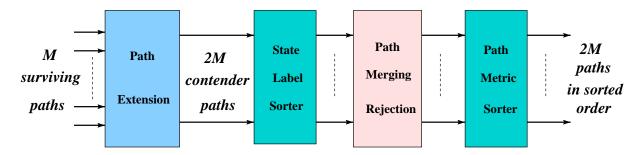

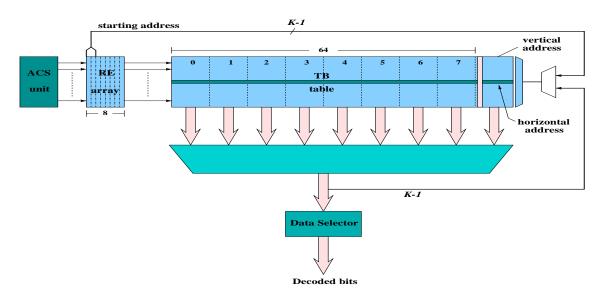

| 5.2  | Block Diagram of the M Algorithm Architecture.                                                                                             | 103 |

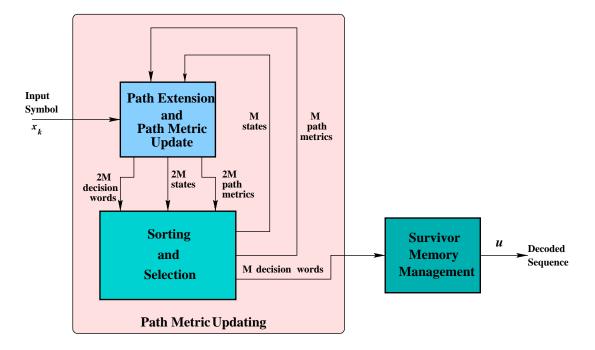

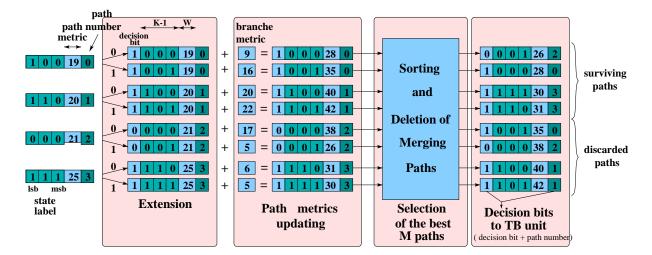

| 5.3  | Architecture for Path Extension.                                                                                                           | 103 |

| 5.4  | Hardware operations performed by the M algorithm at every trellis stage $\vdots$                                                           | 105 |

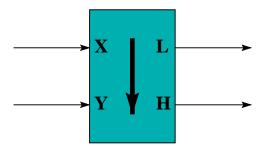

| 5.5  | Comparison-exchange element for sorting networks.                                                                                          | 106 |

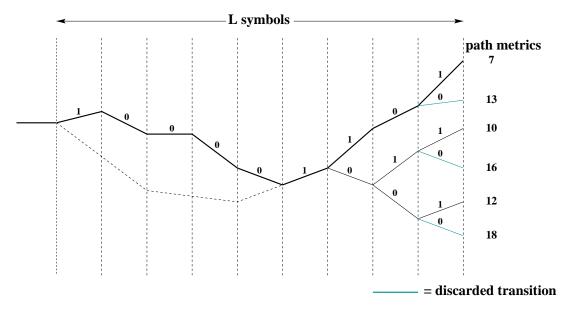

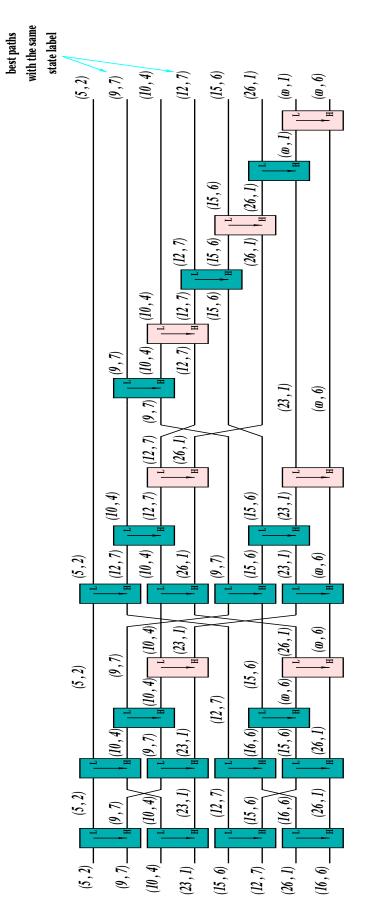

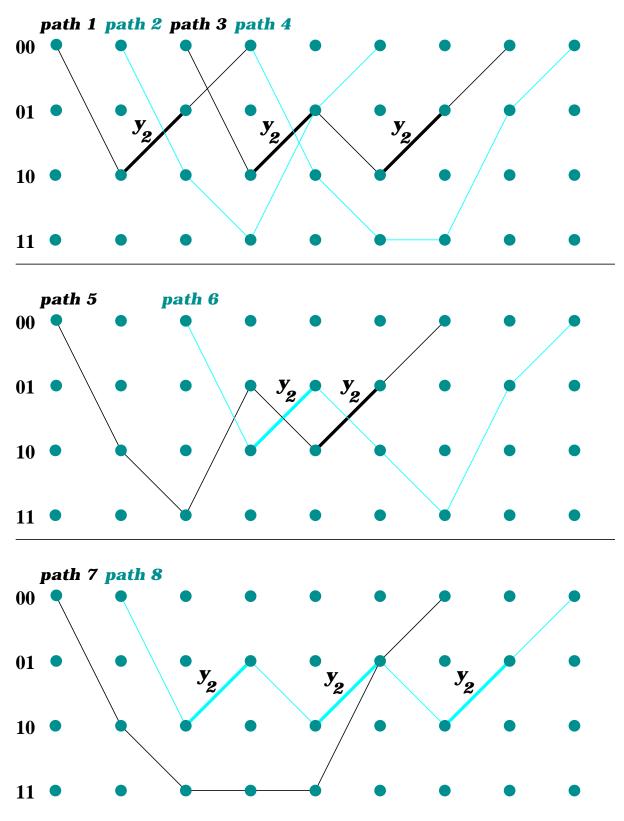

| 5.6  | Merging paths during the construction of the surviving paths (M=3)                                                                         | 107 |

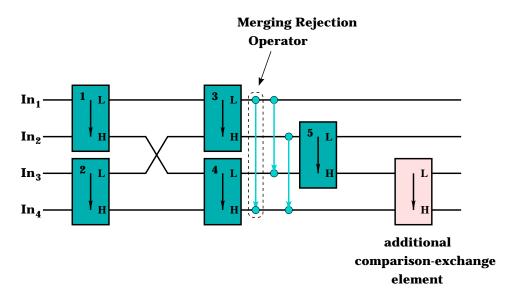

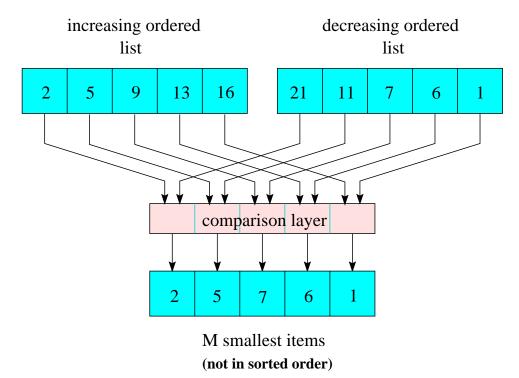

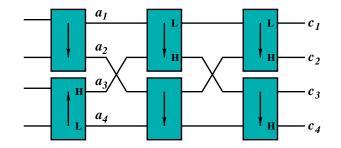

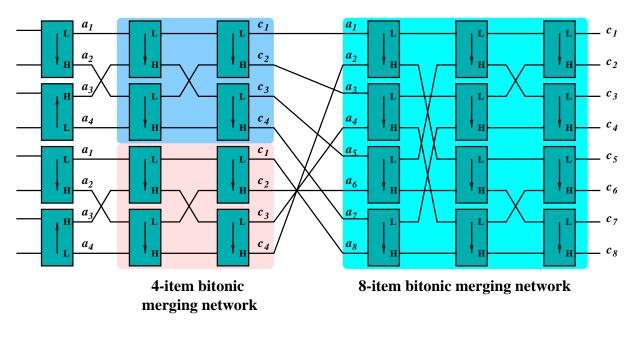

| 5.7  | Path merging rejection in odd-even sorting networks. 4-item structure                                                                      | 108 |

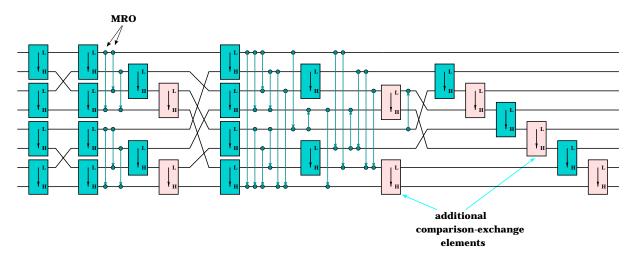

| 5.8  | Path merging rejection in odd-even sorting networks. 8-item structure                                                                      | 109 |

| 5.9  | Mohan and Sood's approach for path merging rejection                                                                                       | 111 |

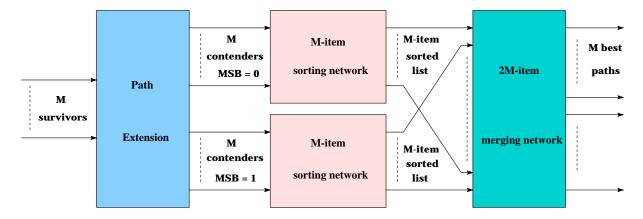

| 5.10 | Separation of the extended paths into two sets for path merging detection.                                                                 | 112 |

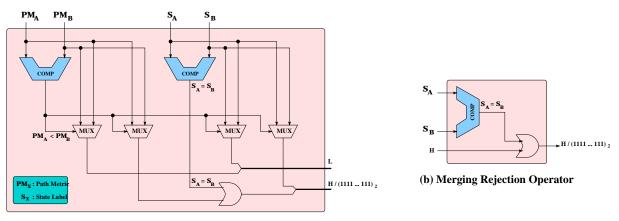

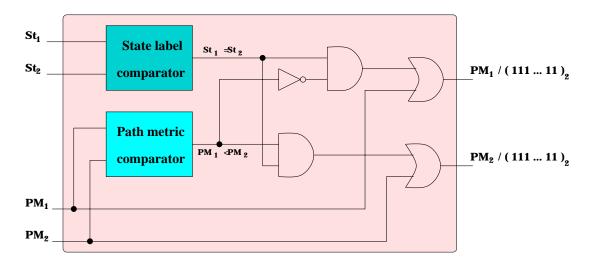

| 5.11 | Internal Structure of the new operators utilized in the sorting network. a) comparison-exchange-saturation; b) merging rejection operator. | 112 |

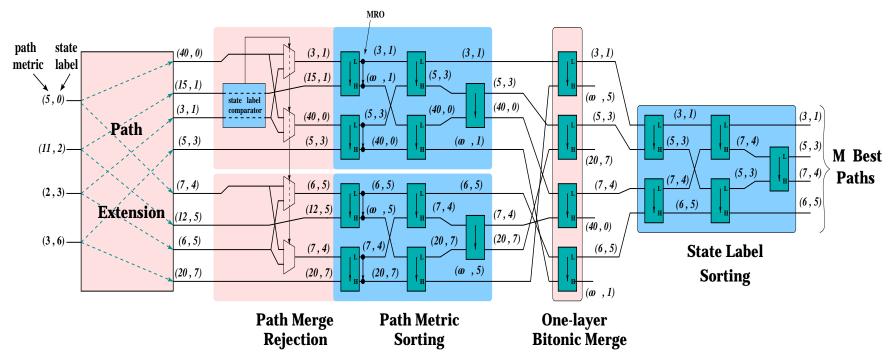

| 5.12 | Odd-even sorting network for $M = 4$ performing simultaneous sorting and path merging rejection.                                           | 113 |

| 5.13 | Odd-even sorting network for $M = 8$ with simultaneous sorting and path merging rejection.                                                 | 115 |

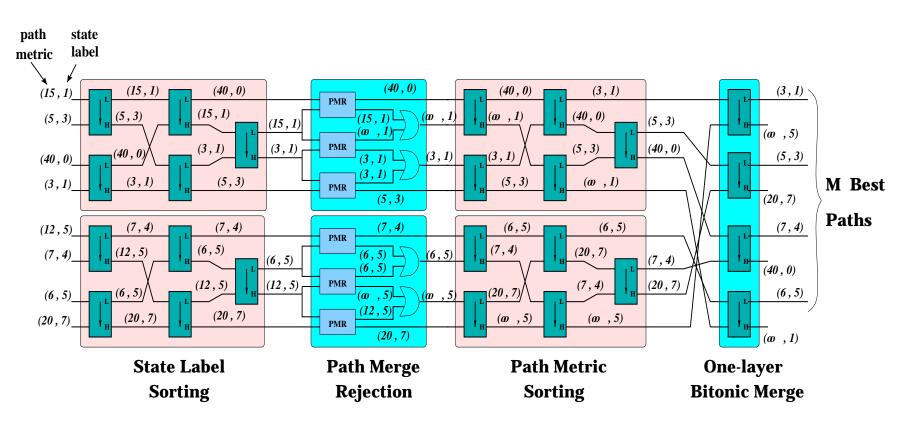

| 5.14 | Block Diagram of the Combined Sorting and Selection Method.                                                                                | 116 |

| 5.15 | Circuit diagram of a path merge rejection cell.                                                                                            | 117 |

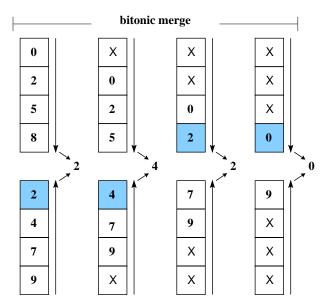

| 5.16 | Selection of the best M paths with a one-layer bitonic merging                                                                             | 118 |

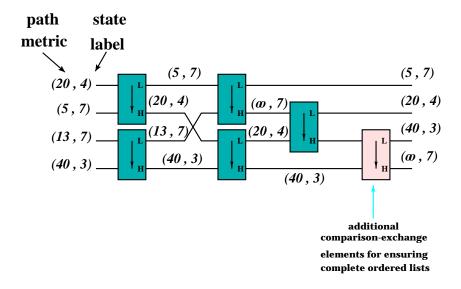

| 5.17 | Sorting Example of the Combined Sorting and Selection Method.                                                                              | 119 |

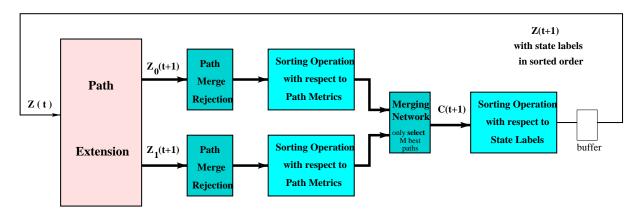

| 5.18 | Block Diagram of the Delayed State Label Sorting Method                                                                                    | 123 |

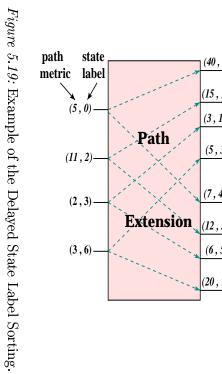

| 5.19 | Example of the Delayed State Label Sorting                                                                                                 | 124 |

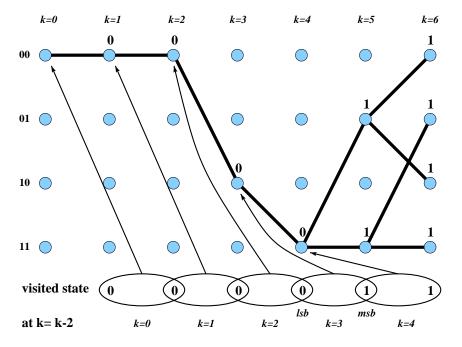

| 5.20 | Example of the Trace-Back procedure in Viterbi decoders.                                                                                   | 128 |

| 5.21 | Wrong Trace-Back Procedure in the M algorithm.                                                                                             | 130 |

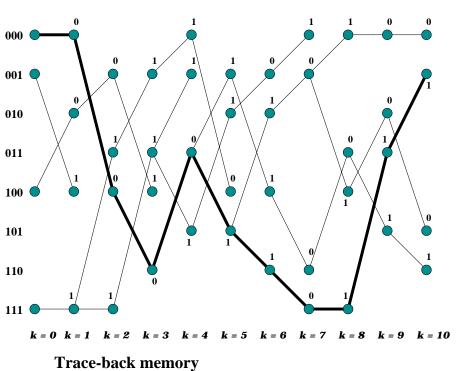

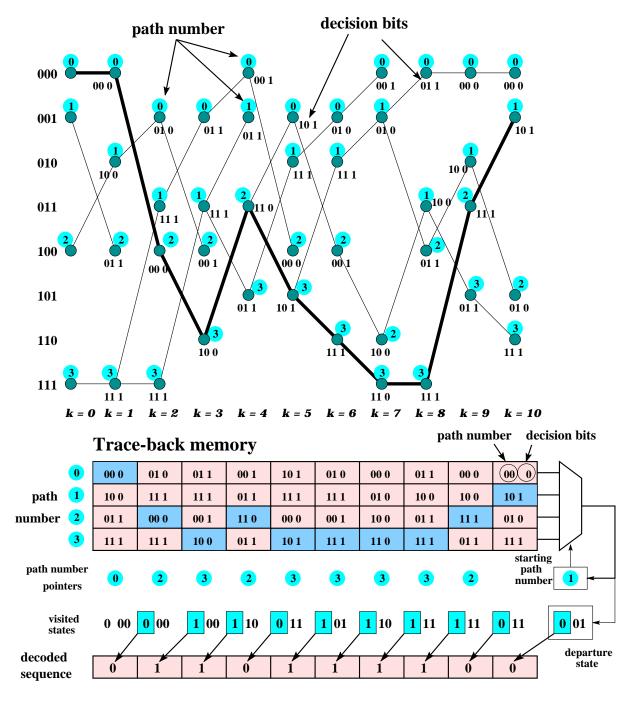

| 5.22 | Trace-Back by comparison of visited states                                                                                                 | 131 |

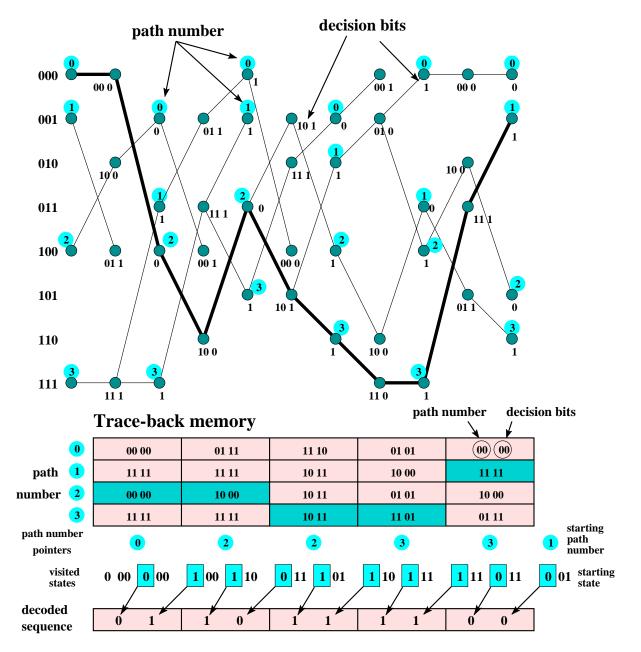

| 5.23 | Pointer generation for TB decoding                                                                                                         | 133 |

| 5.24 | Trace-Back with Path-Number Pointer                                                                                                        | 134 |

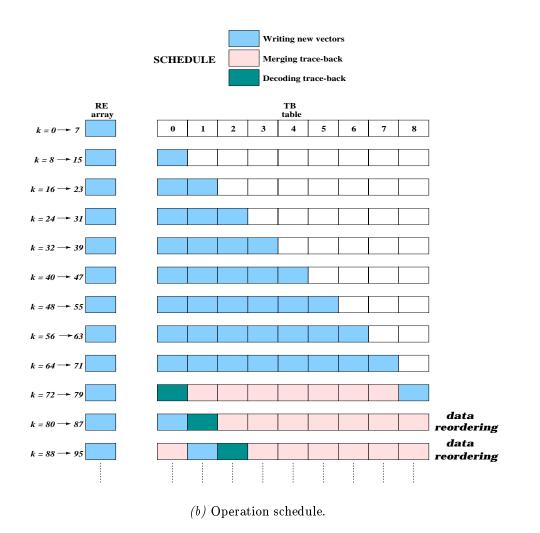

| 5.25 | Operation example of a block trace-back adapted to the M algorithm :                                                                       | 137 |

| 5.26 | Forward Trace-back architecture for the M algorithm.                                                                                       | 139 |

| 5.27 | Simultaneous parallel insertion and bitonic merging of path metrics                                                                        | 143 |

| 6.1  | Joint Source-Channel Trellis Coding Scheme                                                                                                 | 147 |

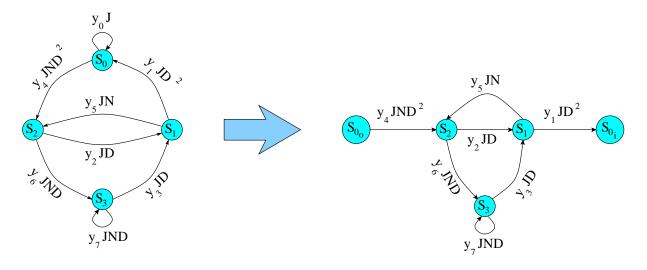

| 6.2  | State transition diagram for a joint trellis source code and rate $1/2$ , K=3 convolutional code                                           | 151 |

| 6.3  | First paths of expression $6.10$                                                                                              | 153 |

|------|-------------------------------------------------------------------------------------------------------------------------------|-----|

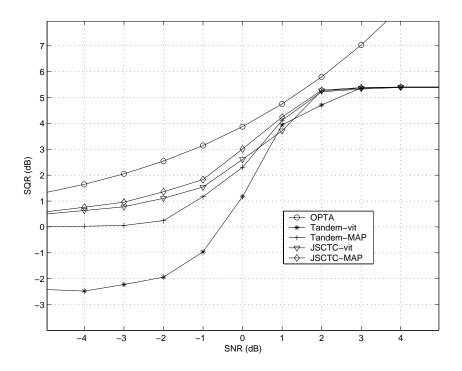

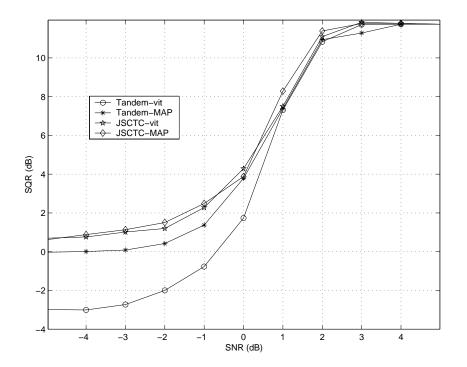

| 6.4  | Performance comparison between the proposed system and a tandem scheme for a gaussian source and AWGN channel.                | 159 |

| 6.5  | Performance comparison between the proposed system and a tandem scheme for a first order gauss-markov source and AWGN channel | 159 |

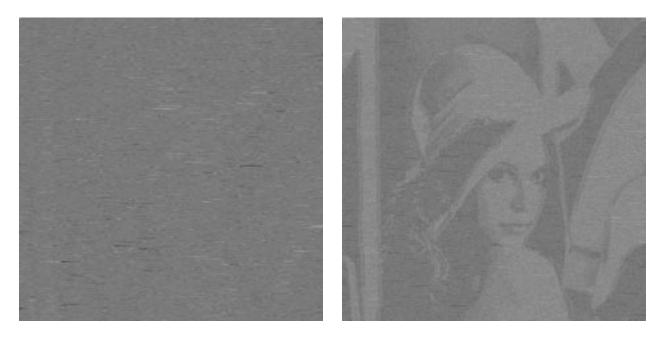

| 6.6  |                                                                                                                               | 160 |

| 6.7  |                                                                                                                               | 160 |

| 6.8  |                                                                                                                               | 161 |

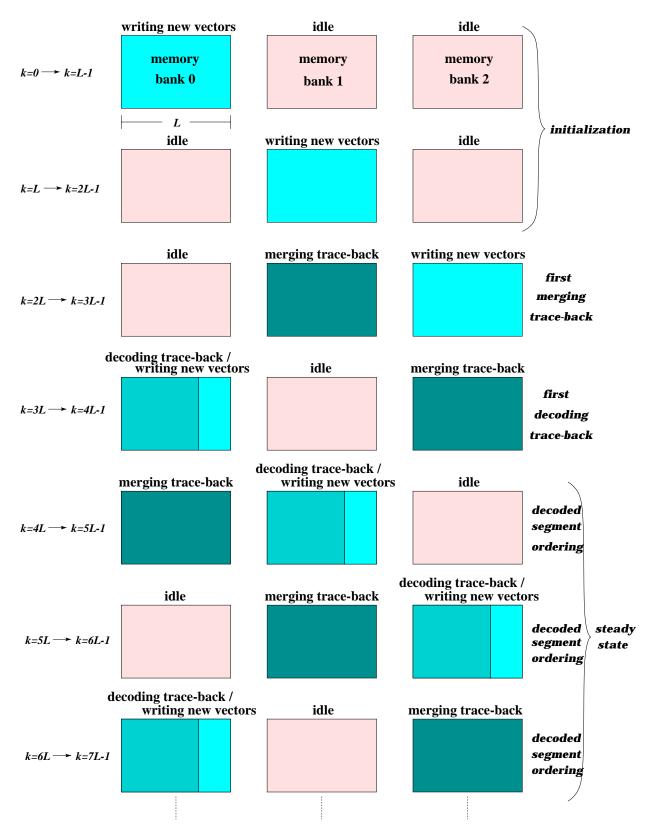

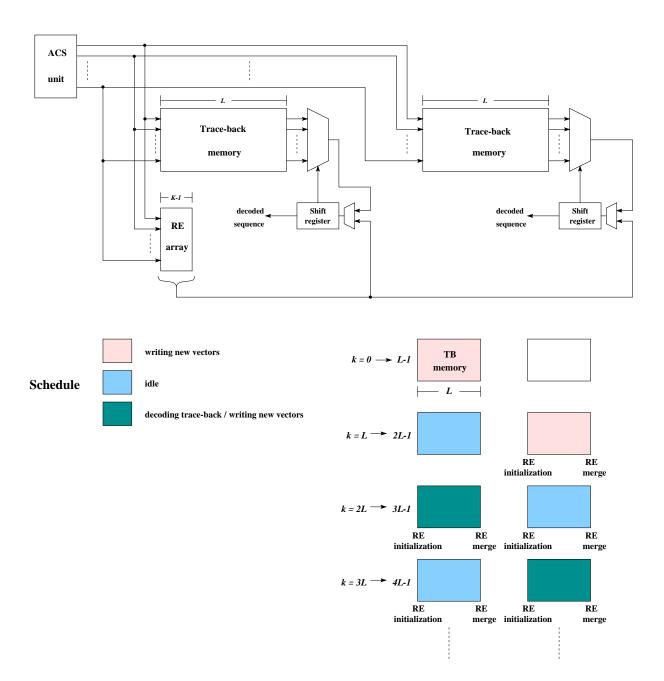

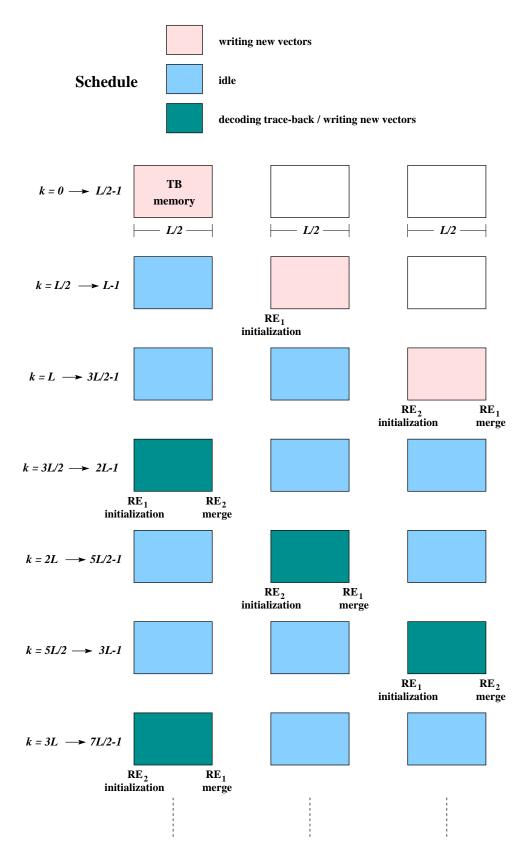

| A.1  | Trace-back schedule for a 2-pointer trace-back                                                                                | 169 |

| A.2  | Ancestor state property of the surviving paths                                                                                | 171 |

| A.3  | Block trace-back architecture and operations schedule. $\ldots$                                                               | 173 |

| A.4  | Register-Exchange-Pointer Trace-Back Architecture and Operations Sched-<br>ule                                                | 175 |

| A.5  | Register-Exchange-Pointer Trace-Back Schedule with two RE pointers. $\ . \ .$                                                 | 176 |

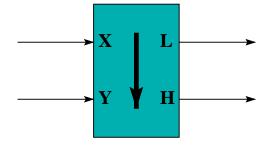

| B.1  | Comparison-exchange element for sorting networks.                                                                             | 180 |

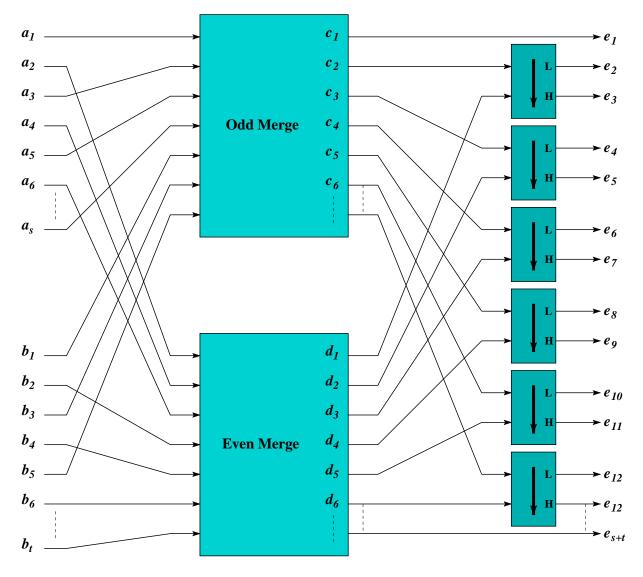

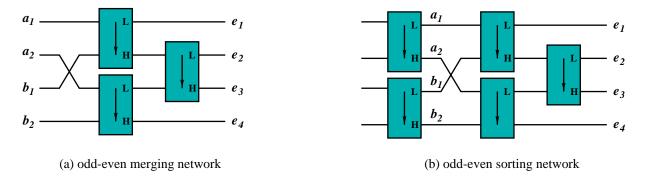

| B.2  | Iterative rule of the odd-even merging network.                                                                               | 181 |

| B.3  | Four-item merging and sorting networks                                                                                        | 182 |

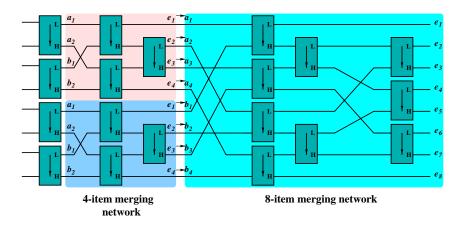

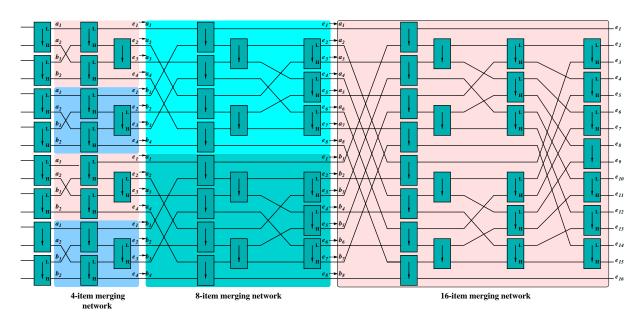

| B.4  | Odd-even sorting networks for $N=8$ and $N=16$ -item lists                                                                    | 183 |

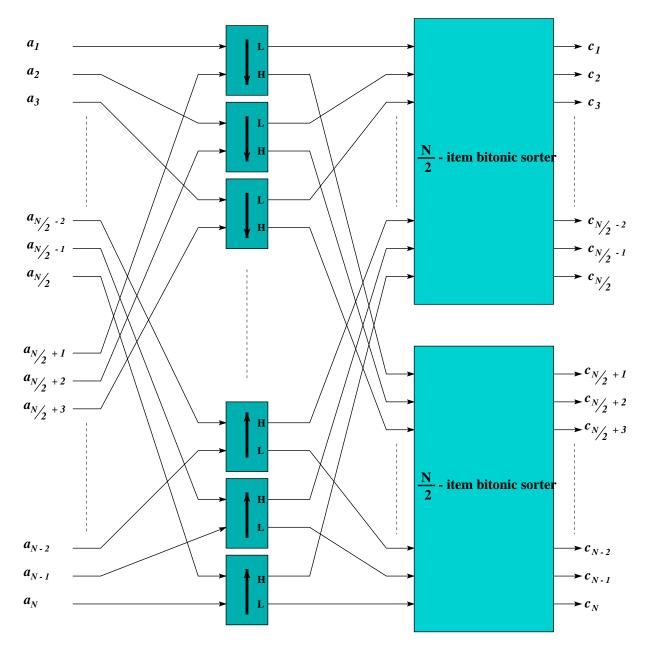

| B.5  | Iterative rule for the bitonic merging network.                                                                               | 185 |

| B.6  | Bitonic sorting networks for four and eight item lists                                                                        | 186 |

| B.7  | Bubble sorting network for 16-item lists                                                                                      | 187 |

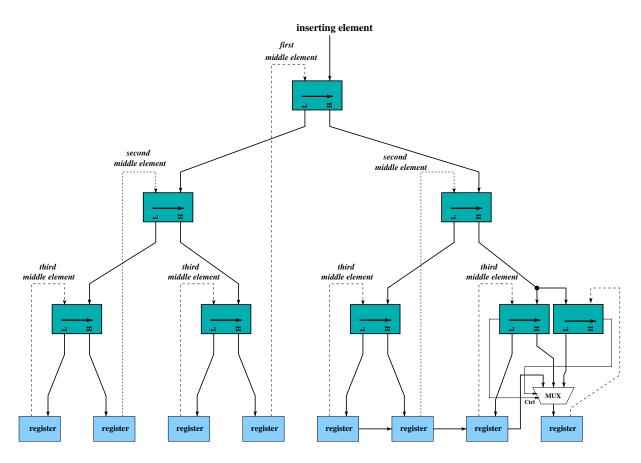

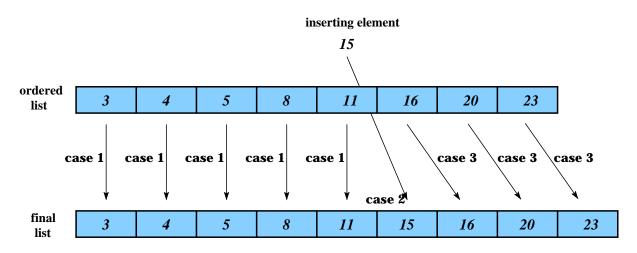

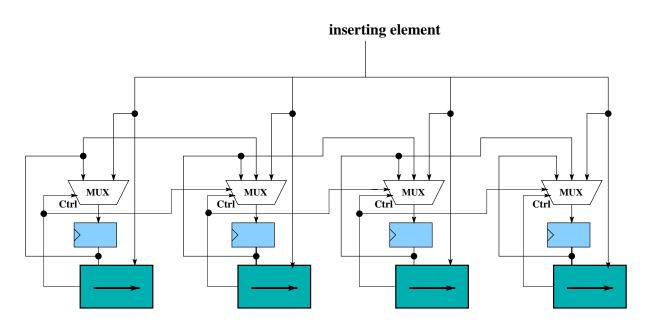

| B.8  | Sorting architecture with the single insertion algorithm                                                                      | 188 |

| B.9  | Sorting architecture with the dichotomic insertion algorithm                                                                  | 189 |

| B.10 | Principle of parallel insertion.                                                                                              | 190 |

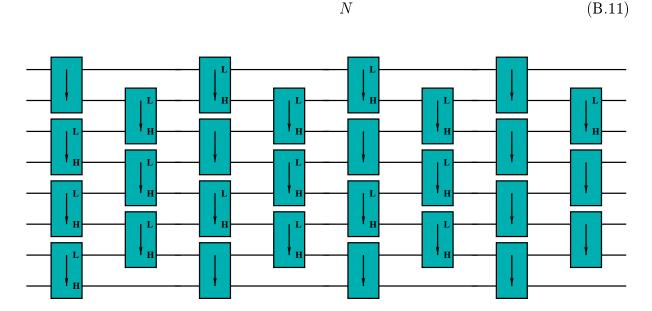

| B.11 | Parallel insertion Architecture.                                                                                              | 191 |

## List of Tables

| 3.1 | Computational requirements of the distortion measure in the JSCTC algo-<br>rithm                                                                         |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2 | Codebook Design Latency of Architectures 1 and 2                                                                                                         |

| 3.3 | Latency comparison between architectures 1 and 2                                                                                                         |

| 4.1 | Estimation of the computational load per input symbol of the Viterbi and M algorithms                                                                    |

| 4.2 | Performance degradation introduced by the suboptimum trellis search $90$                                                                                 |

| 5.1 | Comparison-exchange elements used in the combined sorting and selection<br>method and in Mohan and Sood's approach                                       |

| 5.2 | Comparison-exchange elements used in the proposed method and in Mohan<br>and Sood's combined sorting and selection                                       |

| 5.3 | Architecture latency of the combined sorting and selction method and Mohan and Sood's approach.                                                          |

| 5.4 | Hardware complexity comparison between the delayed state label sorting network, the combined sorting and selection method and Mohan and Sood's approach. |

| 5.5 | Storage Requirements of the Viterbi and M algorithms                                                                                                     |

| 5.6 | Viterbi and M Algorithm Computational Load for Branch Metric Compu-<br>tation and Path Metric Updating                                                   |

| 6.1 | Simulated and estimated pairwise error probabilites for SNR=0 and 1 dB $$ . 154                                                                          |

| 6.2 | Simulated and estimated pairwise error probabilites for SNR=2 and 3 dB $$ . 154                                                                          |

| A.1 | Latency and storage requirements of the different survivor memory man-<br>agement techniques                                                             |

## Introduction

The main goal of a digital communication system consists in both looking for efficient ways to represent the information to be transmitted and to render this representation robust to the corrupting effects of the transmission channel. The usual approach to accomplish these two goals is the well known "divide et impera" principle: the information transmission problem is divided into two tasks, source coding and channel coding. The former seeks to represent the information to be transmitted with the least possible number of bits whereas the latter must guarantee a reliable communication between the transmitter and the receiver. This is achieved by introducing additional information to the compressed source so that the receiver can recover the original information from a compressed and noise-corrupted version of it.

This task separation is due to Shannon's pioneering work which stablished the foundations of what is now known as Information Theory. C. E. Shannon demonstrated that, under certain assumptions, this separation allows the design of optimum-performance communication systems. Nowadays, we witness the optimality of these assumptions. Indeed, today's advances in both information theory and semiconductor technology permit the design of communication systems which allow in turn to transmit information with performances that approach the theoretical limits predicted by Shannon's work. These systems have reached a certain maturity that has dramatically increased the services that can be provided by them. Satellite and mobile communications, internet and mutimedia applications have had an amazing development in the last five years thanks to the great advances in source and channel coding. Source coders such as vocoders, CELP coders, JPEG, MPEG2 and MPEG4 standards; and channel coding tecniques such as coded modulation, turbo codes, turbo-equalization and code division multiple access, constitute few examples of the potential techniques which facilitate the approach towards the Shannon limits.

Nevertheless, this apogee in the services provided by present time communication systems causes in turn a strong demand to make data transmission more efficient and provide greater performance. In particular, environments such as mobile satellite systems require minimal power usage and minimal bandwidth usage to maximize the number of users, which restricts the use of channel coding. On the other hand, its time-varying nature causes bursty errors which, if mitigated by interleaving, would induce lengthy delays. As a consequence, it seems that communication systems design is close to its upper limit. This is because Shannon's separability theorem has been used as a design principle, motivating always the concatenation of separately optimized source and channel coders. However, the theorem assumes that the source coder is an optimal one that removes all source redundancy. Moreover, it assumes that for rates below channel capacity, the channel coder corrects all errors. Such optimal systems can only be achieved in general by allowing limitless encoding/decoding complexity and delay. Practical systems must limit complexity and delay, and thus sacrifice performance. In many cases it is not reasonable to assume then that the conditions for the separation theorem hold even approximately. For instance, for several noisy channels, channel codes may fail to reduce errors and may in fact, increase the bit error rate. Moreover, the output of practical source encoders may contain a significant amount of redundancy, specially for sources with memory such as speech and images. In this circumstances, we can potentially improve performance by considering the souce and channel designs jointly.

Since the late seventies, researchers started to realized this last problem and wondered if a joint design could not lead to more efficient and less complex systems. This question was taken into account more seriously in the following years and Joint Source-Channel Coding was born. Since the last decade, JSCC has attracted so much attention that today, we can find a wide range of applications where the concepts and underlying principles of JSCC are proposed. Nonetheless, these systems are still confined to the pure research stage and no or very little hardware implementations of JSCC systems have been proposed. This thesis is intended to start contemplating the possibility of designing hardware architectures for JSCC.

In particular, this thesis is concerned with the design of hardware architectures for Joint Source-Channel Trellis Coding. This technique consists in the design of trellis quantization algorithms that are robust to channel errors. The main characteristic of this technique is that source and channel protection are indeed merged into a single operation. The goal of this system is the complete elimination of the channel coding scheme or at least to reduce its hardware complexity. With this approach we seek new alternatives to the conventional tandem scheme, presenting a reduced hardware complexity system, with a smooth degradation of its overall performance, as opposed to the tandem system where the optimality is obtained for a very small range of channel conditions.

The methodology employed in this thesis consisted in three main parts. First, a study on the hardware requirements of the JSCTC technique was peformed, and a comparison to conventional systems was done from both performance and complexity standpoints. Then, suboptimal architectures were studied which allow a significant reduction in the hardware complexity while maintaining the overall performance as close as possible to the optimum system. This way, its hardware implementation in medium- to low-complexity circuits such as digital signal processors, field programmable gate arrays, etc. can be accomplished. Finally, the third step consisted in further studying this technique, this time from a theoretical point of view, in order to seek for other means to improve its overall performance. This work is a continuation of a series of research activities at the COMELEC department focused on JSCC.

#### Thesis Outline