### THESE DE DOCTORAT DE

#### L'UNIVERSITE BRETAGNE SUD

COMMUE UNIVERSITE BRETAGNE LOIRE

ECOLE DOCTORALE N° 601

Mathématiques et Sciences et Technologies

de l'Information et de la Communication

Spécialité: (voir liste des spécialités)

Par

#### **Hassan Harb**

# Conception du décodeur NB-LDPC à débit ultra-élevé

Thèse présentée et soutenue à Lorient, le 08-11-2018

Unité de recherche : Lab-STICC UMR 6285

Thèse N°: 504

#### Rapporteurs avant soutenance :

ANDREAS Burg Assistant Professeur, Ecole Polytechnique Fédérale de Lausanne

ZHENGYA Zhang Assistant Professeur, University of Michigan

#### **Composition du Jury:**

Président : Olivier Berder Professeur, IUT Lannion

Examinateurs : Catherine Douillard Professeur, Dept. Electronique, IMT Atlantique Dir. de thèse : Emmanuel Boutillon Professeur, Lab-STICC Université de Bretagne Sud

Co-dir. de thèse : Laura Conde-Canencia Assistant Professeur, Lab-STICC Université de Bretagne Sud

Invité

Bertrand Le Gal Assistant Professeur, IMS Lab Bordeaux

Titre: Conception du décodeur NB-LDPC à débit ultra-élevé

Mots clés: NB-LDPC, H-CN, VN, FTSES.

**Résumé**: Les codes correcteurs d'erreurs Non-Binaires Low Density Parity Check (NB-LDPC) sont connus pour avoir de meilleure performance que les codes LDPC binaires. Toutefois, la complexité de décodage des codes non-binaires est bien supérieure à celle des codes binaires. L'objectif de cette thése est de proposer de nouveaux algorithmes et de nouvelles architectures matérielles de code NB-LDPC pour le décodage des NBLDPC. La première contribution de cette thése consiste à réduire la complexité du noeud de parité en triant en amont ses messages d'entrées. Ce tri initial permet de rendre certains états très improbables et le matériel requis pour les traiter peut tout simplement être supprimé. Cette suppression se traduit directement par une reduction de la complexité du décodeur NB-LDPC, et ce, sans affecter significativement les performances de décodage.

Un modéle d'architecture, appelée "architecture hybride" qui combine deux algorithmes de l'état de l'art ("l'Extended Min Sum" et le "Syndrome Based") a été proposé afin d'exploiter au maximum le pré-tri. La these propose aussi de nouvelles méthodes pour traiter les noeuds de variable dans le context d'une architecture pré-tri. Différents exemples d'implémentations sont donnés pour des codes NB-LDPC sur GF(64) et GF(256). En particulier, une architecture très efficace de décodeur pour un code de rendement 5/6 sur GF(64) est présentée. Enfin, une problématique récurrente dans les architectures NB-LDPC, qui est la recherche des P minimums parmi une liste de taille N<sub>s</sub>, est abordée. La thése propose une architecture originale appelée first-then-second minimum pour une implantation efficace de cette tâche.

**Title:** Design of ultra high throughput rate NB-LDPC decoder

**Keywords:** NB-LDPC, H-CN, VN, FTSES.

**Abstract** The Non-Binary Low Density Parity Check (NB-LDPC) codes constitutes an interesting category of error correction codes, and are well known to outperform their binary counterparts. However, their non-binary nature makes their decoding process of higher complexity. This PhD thesis aims at proposing new decoding algorithms for NB-LDPC codes that will be shaping the resultant hardware architectures expected to be of low complexity and high throughput rate. The first contribution of this thesis is to reduce the complexity of the Check Node (CN) by minimizing the number of messages being processed. This is done thanks to a pre-sorting process that sorts the messages intending to enter the CN based on their reliability values, where the less likely messages will be omitted and consequently their dedicated hardware part will be simply removed. This reliability-based sorting enabling the processing of only the highly reliable messages induces a high reduction of the hardware complexity of the NB-LDPC decoder. Clearly, this hardware reduction must come at no significant performance degradation. A new Hybrid architectural CN model (H-CN) combining two state-of-the-art algorithms - Forward-Backward CN (FB-CN) and Syndrome Based CN (SB-CN) - has been proposed.

This hybrid model permits to effectively exploit the advantages of pre-sorting.

This thesis proposes also new methods to perform the Variable Node (VN) processing in the context of pre-sorting-based architecture. Different examples of implementation of NB-LDPC codes defined over GF(64) and GF(256) are presented. For decoder to run faster, it must become parallel. From this perspective, we have proposed a new efficient parallel decoder architecture for a 5/6 rate NB-LDPC code defined over GF(64). This architecture is characterized by its fully parallel CN architecture receiving all the input messages in only one clock cycle. The proposed new methodology of parallel implementation of NB-LDPC decoders constitutes a new vein in the hardware conception of ultra-high throughput rate decoders. Finally, since the NB LDPC decoders requires the implementation of a sorting function to extract P minimum values among a list of size N<sub>s</sub>, a chapter is dedicated to this problematic where an original architecture called First-Then-Second-Extrema-Selection (FTSES) has been proposed.

### Acknowledgement

It is my honor to present this work for my parents who encouraged and supported me.

I am thankful for who trusted and chose me to be the one who works with them, I mean Dr. Ali Al Ghouwayel, Prof. Emmanuel Boutillon, Prof. Ali Alaedine and Dr. Laura Conde-Canencia. Fruitful discussions of experiments with them are gratefully acknowledged. With them, I knew what devotion, dedication, determination and discipline mean. Their company taught me how to perform knowledge in a real technical work.

Sincerely, I highly appreciate the dedicated and effective effort and ideas that were proposed by Dr. Cédric Marchand to make this work successful.

Of course I cannot but thank Dr. Bertarnd Le Gal for the unforgettable knowledge and care he provided me during my accommodation in Bordeaux, where I learned a new tool that was extremely useful to complete this work and it will be helpful in my future.

The authors would like to acknowledge the valuable comments and suggestions of the reviewers Prof. Zhang Zhengya and Prof. Andreas Burg, which have improved the quality of this work.

The authors would like to acknowledge the jury members Prof. Olivier Berder and Prof. Catherine Douillard who paid attention for our work and gave us their precious time to have fruitful and objective discussion with them.

Hassan HARB.

# Contents

| $\mathbf{C}$  | onter | $_{ m nts}$    |                                                            | ę               |

|---------------|-------|----------------|------------------------------------------------------------|-----------------|

| $\mathbf{Li}$ | st of | Figur          | es                                                         | 13              |

| $\mathbf{Li}$ | st of | Table          | ${f s}$                                                    | 17              |

| 1             | Intr  | coduct         | ion                                                        | 1               |

| 2             | ture  | es             | C codes: Principles, Decoding Algorithms and Architecture  | 5               |

|               | 2.1   |                | Sinary LDPC codes defined on a Galois field                | 5               |

|               | 2.2   |                | ive decoding algorithms for NB-LDPC codes                  | 1.0             |

|               |       | 2.2.1          | BP algorithm                                               | 10              |

|               |       | 2.2.2 $2.2.3$  | Log-BP algorithm                                           | 11              |

|               |       | 2.2.3 $2.2.4$  | Min-Sum algorithm                                          | $\frac{12}{12}$ |

|               |       | 2.2.4 $2.2.5$  | EMS algorithm and its variants                             | $\frac{1}{4}$   |

|               | 2.3   |                | Min-Max algorithm                                          | $\frac{14}{15}$ |

|               | ۷.۵   | гв аг<br>2.3.1 | nd SB CNs algorithms                                       |                 |

|               |       | 2.3.1 $2.3.2$  | Forward-Backward CN processing                             | $\frac{15}{17}$ |

|               |       | 2.3.2 $2.3.3$  | Syndrome-based CN processing                               |                 |

|               | 2.4   |                | Presorting                                                 | $\frac{19}{21}$ |

|               | 2.4   | 2.4.1          | iption of an existing VN architecture                      | 21              |

|               |       | 2.4.1          | An example of the VN functionality                         |                 |

|               |       |                | 2.4.1.1 An example in update mode                          | 21              |

|               |       | 0.40           | 2.4.1.2 An example in decision mode                        | 22              |

|               |       | 2.4.2          | VN architecture in update mode                             | 23              |

|               |       | 0.4.0          | 2.4.2.1 Architecture of the Sorter block                   | 24              |

|               |       | 2.4.3          | VN architecture in the decision-making mode                | 26              |

|               | 2.5   |                | ed vs. Flooding decoder scheduling                         | 28              |

|               | 2.6   |                | of-the-art NB-LDPC decoder architectures                   | 29              |

|               |       | 2.6.1          | A fully parallel NB-LDPC decoder with fine-grained dynamic | 0.0             |

|               |       |                | clock gating                                               | 29              |

|               |       | 2.6.2          | Trellis-Based extended Min-Sum algorithm Decoder           | 3(              |

10 contents

|   |         | 2.6.3             |                   | Gbps Non-Binary LDPC decoder for high-speed comions           |

|---|---------|-------------------|-------------------|---------------------------------------------------------------|

|   | 2.7     | Concl             |                   |                                                               |

| _ | <b></b> |                   |                   |                                                               |

| 3 |         |                   |                   | ares for NB-LDPC decoding                                     |

|   | 3.1     |                   |                   | le Architectures                                              |

|   |         | 3.1.1             |                   | with presorting                                               |

|   |         | 3.1.2             | <del>-</del>      | d FB-CN Architecture                                          |

|   |         |                   | 3.1.2.1           | Sorter                                                        |

|   |         |                   | 3.1.2.2           | Switch                                                        |

|   |         |                   | 3.1.2.3           | Simplified ECNs                                               |

|   |         |                   | 3.1.2.4           | ECN simplifications for global CN with different $d_c$ values |

|   |         | 3.1.3             | Impleme           | entation and simulation results                               |

|   |         | 0.2.0             | 3.1.3.1           | Implementation results                                        |

|   |         |                   | 3.1.3.2           | Simulation results                                            |

|   |         | 3.1.4             |                   | d Forward and hybrid CN                                       |

|   |         | 0.1.1             | 3.1.4.1           | Syndrome computation using the EF processing                  |

|   |         |                   | 3.1.4.2           | EF CN with presorting                                         |

|   |         |                   | 3.1.4.3           | The Syndrome Node                                             |

|   |         |                   | 3.1.4.4           | Hybridization between FB and EF CN architectures              |

|   |         |                   | 3.1.4.5           | General notations for hybrid architectures                    |

|   |         |                   | 3.1.4.6           | Choice of parameters $(\rho_{SN}, \rho_{EF}, \rho_{FB})$      |

|   |         |                   | 3.1.4.7           | Suppression of final output RE                                |

|   |         | 3.1.5             |                   | ance and complexity analysis                                  |

|   |         | 0.1.0             | 3.1.5.1           | Performance                                                   |

|   |         |                   | 3.1.5.2           | Implementation results                                        |

|   |         |                   | 3.1.5.2           | Area and energy efficiency comparison                         |

|   |         |                   | 3.1.5.4           | Throughput                                                    |

|   |         | 3.1.6             |                   | Processing Controller (SPC)                                   |

|   | 3.2     |                   | -                 | tecture                                                       |

|   | 9.2     | 3.2.1             |                   | d VN architecture                                             |

|   |         | 5.2.1             | 3.2.1.1           | VNP in update mode                                            |

|   |         |                   | 3.2.1.1 $3.2.1.2$ | Proposed architecture of the decision-making circuit          |

|   |         | 3.2.2             |                   | entation results                                              |

|   | 3.3     |                   | -                 |                                                               |

|   | ა.ა     | Conci             | usion             |                                                               |

| 4 |         | allel p<br>algor: | _                 | architectures: LLR generator and extrema selec                |

|   | 4.1     | 0                 |                   | ed LLR generator                                              |

|   |         | 4.1.1             |                   | on of the LLRs                                                |

|   |         | 4.1.2             |                   | d architecture                                                |

|   |         | <b></b>           | 4.1.2.1           | Parallel sorting of the channel observations                  |

|   |         |                   | 4.1.2.2           | Design of the pre-defined set of potential candidates         |

|   |         |                   |                   | o r see of personal confidences                               |

contents 11

|   |     |               | 4.1.2.3 Sorting of the potential candidates 6               |

|---|-----|---------------|-------------------------------------------------------------|

|   |     |               | 4.1.2.4 Inverse permutation of the GF values of $J^s$ 68    |

|   |     | 4.1.3         | Complexity analysis                                         |

|   |     | 4.1.4         | Example for $n_m = 4$                                       |

|   | 4.2 | Parall        | el pipelined architecture for extrema selection algorithm 7 |

|   |     | 4.2.1         | Problem Statement and Proposed Algorithm                    |

|   |     |               | 4.2.1.1 Algorithm                                           |

|   |     |               | 4.2.1.2 Architecture of $N_s$ -SU for $N_s = 8 \dots 7$     |

|   |     | 4.2.2         | Proposed $N_s$ -SU Architecture: Complexity and Performance |

|   |     |               | Analysis                                                    |

|   |     |               | 4.2.2.1 Global $N_s$ -SU Architecture                       |

|   |     |               | 4.2.2.2 Complexity Analysis                                 |

|   |     |               | 4.2.2.3 Timing Analysis                                     |

|   |     |               | 4.2.2.4 Discussion                                          |

|   |     | 4.2.3         | Hardware Implementation                                     |

|   |     |               | 4.2.3.1 Implementation Results                              |

|   |     |               | 4.2.3.2 Area and power efficiency comparison                |

|   |     | 4.2.4         | Extension of the proposed sorter                            |

|   | 4.3 | Concl         | usion                                                       |

| 5 | Dro | bosod         | parallel and pipelined decoder 88                           |

| J | 5.1 |               | structure and decoding algorithm                            |

|   | 0.1 | 5.1.1         | Code Structure                                              |

|   |     | 5.1.1 $5.1.2$ | Decoding algorithm                                          |

|   |     | 5.1.2 $5.1.3$ | Simulation results                                          |

|   | 5.2 |               | sectural overview                                           |

|   | J.∠ | 5.2.1         | Memorization system                                         |

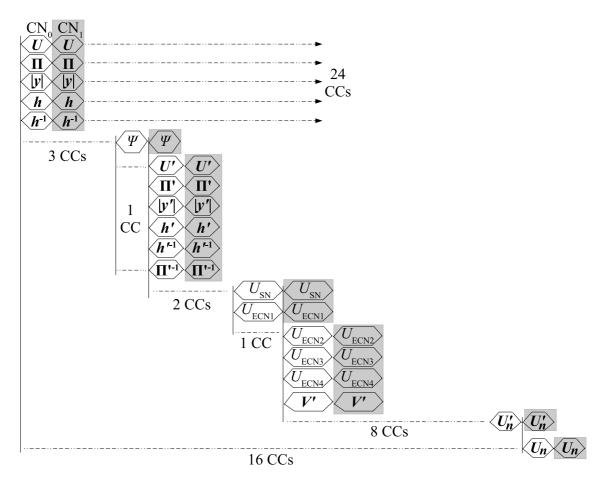

|   |     | 5.2.1 $5.2.2$ | Timing diagram of the overall decoder                       |

|   | 5.3 |               | er components architecture                                  |

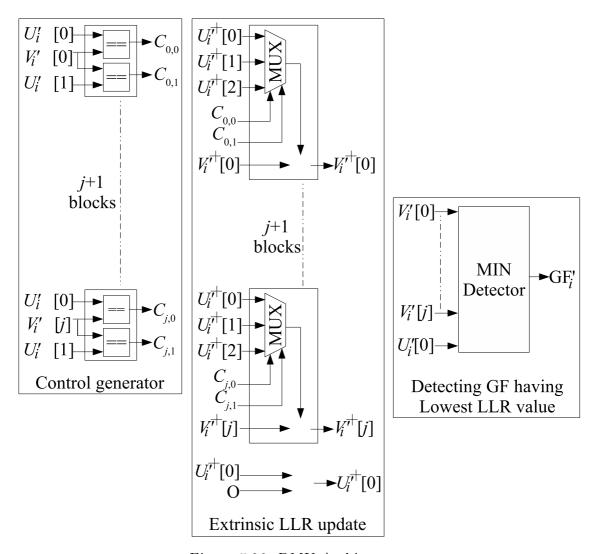

|   | 0.0 | 5.3.1         | The CN-VN block                                             |

|   |     | 0.0.1         | 5.3.1.1 Presorting architecture                             |

|   |     |               | 5.3.1.2 Switching + Multiplication                          |

|   |     |               |                                                             |

|   |     |               | • /                                                         |

|   |     |               | 1                                                           |

|   |     |               | ,                                                           |

|   |     |               |                                                             |

|   |     |               | 5.3.1.7 VN architecture                                     |

|   |     |               | 5.3.1.8 NR architecture                                     |

|   |     | <b>.</b>      | 5.3.1.9 Timing diagram of the CN-VN unit                    |

|   |     | 5.3.2         | DMU architecture                                            |

|   | F 4 | 5.3.3         | PTB                                                         |

|   | 5.4 |               | g diagram of the global decoding process                    |

|   | 5.5 | -             | mentation results                                           |

|   | 5.6 | Hardv         | v are emulation                                             |

| 12 |  | contents |

|----|--|----------|

|    |  |          |

| 6  | Cor   | clusio | and perspectives                                  | 139 |

|----|-------|--------|---------------------------------------------------|-----|

| U  |       |        | Ision                                             |     |

|    |       |        |                                                   |     |

|    | 6.2   | Perspe | ectives                                           | 141 |

| 7  | App   | oendix | A                                                 | 143 |

|    | A.1   | Introd | uction of the Galois field                        | 143 |

|    |       | A.1.1  | Algebraic structures                              | 143 |

|    |       | A.1.2  | The groups                                        | 144 |

|    |       | A.1.3  | The rings                                         | 145 |

|    |       | A.1.4  | Congruence and modular arithmetic in $\mathbb{Z}$ | 145 |

|    |       | A.1.5  | Galois field                                      | 146 |

|    |       | A.1.6  | The polynomials on $GF(q)$                        | 147 |

|    |       | A.1.7  | Construction of the Galois field $GF(2^m)$        | 148 |

| ъ: | blice | graphy |                                                   | 153 |

# List of Figures

| 2.1         | A graphic representation of an LDPC code with a bipartite graph 6                                                                                                                                                                                                          |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2         | A graphic representation for a CN in case of NB-LDPC code [7]                                                                                                                                                                                                              |

| 2.3         | The main algorithms for optimal NB-LDPC decoding [7] 9                                                                                                                                                                                                                     |

| 2.4         | S-bubble ECN and generalized S-bubble ECN                                                                                                                                                                                                                                  |

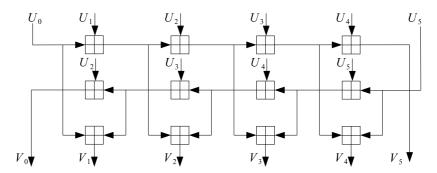

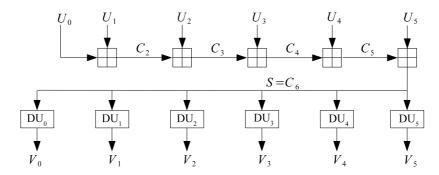

| 2.5         | FB-CN processing with $d_c = 6.$                                                                                                                                                                                                                                           |

| 2.6         | Example of a deviation path                                                                                                                                                                                                                                                |

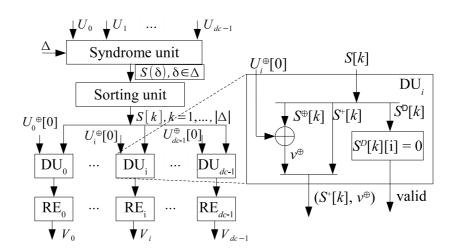

| 2.7         | Syndrome-based CN processing (left part) and details of the DU unit                                                                                                                                                                                                        |

|             | (right part)                                                                                                                                                                                                                                                               |

| 2.8         | Pre-sorting principle                                                                                                                                                                                                                                                      |

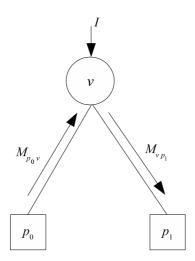

| 2.9         | A VN $v$ connected to two CNs $p_0$ and $p_1$                                                                                                                                                                                                                              |

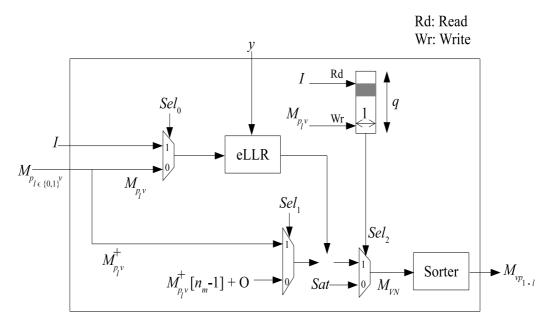

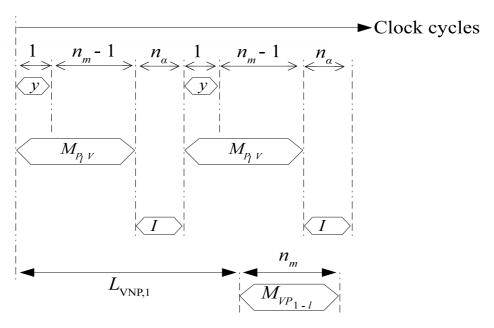

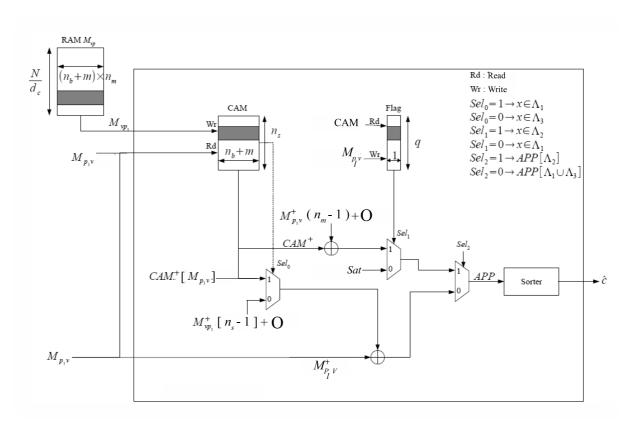

| 2.10        | Architecture of the VN [7] in update mode                                                                                                                                                                                                                                  |

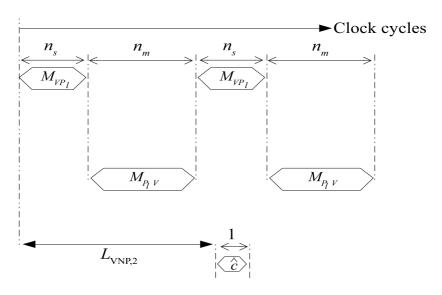

| 2.11        | Timing diagram of VN in update mode [7]                                                                                                                                                                                                                                    |

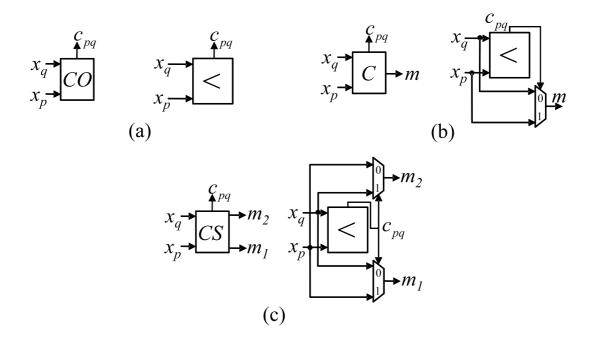

| 2.12        | (a) Comparator Only $(CO)$ , (b) Comparator $(C)$ , (c) Comparator                                                                                                                                                                                                         |

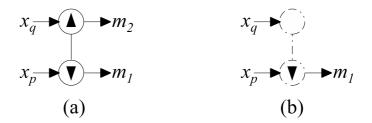

|             | Swap $(CS)$ and $(d)$ ESU $(4\text{-SU})$ Architecture                                                                                                                                                                                                                     |

| 2.13        | (a) $CS$ , (b) $C$                                                                                                                                                                                                                                                         |

| 2.14        | Architecture of the Sorter block [7]                                                                                                                                                                                                                                       |

| 2.15        | VN architecture in decision-making mode (only active blocks are shown) [7]                                                                                                                                                                                                 |

| 2.16        | Timing diagram of VN in decision mode [7]                                                                                                                                                                                                                                  |

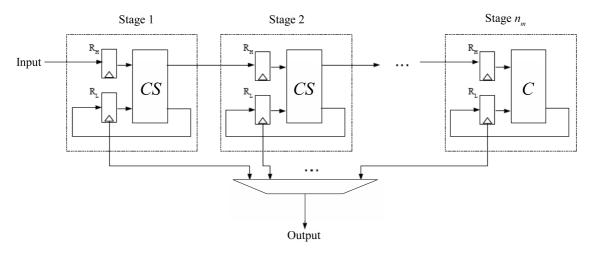

| 2.10 $2.17$ | Stages of processing                                                                                                                                                                                                                                                       |

| 2.11        | Stages of processing                                                                                                                                                                                                                                                       |

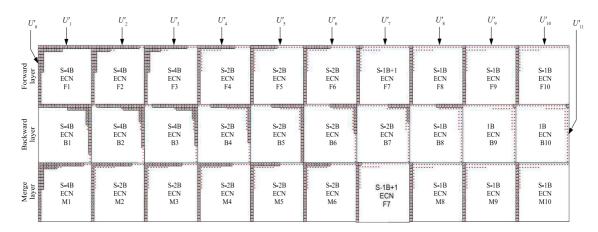

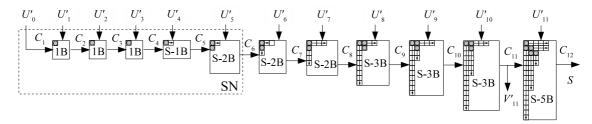

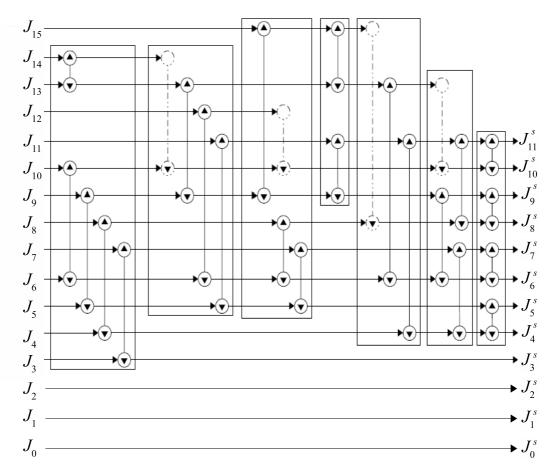

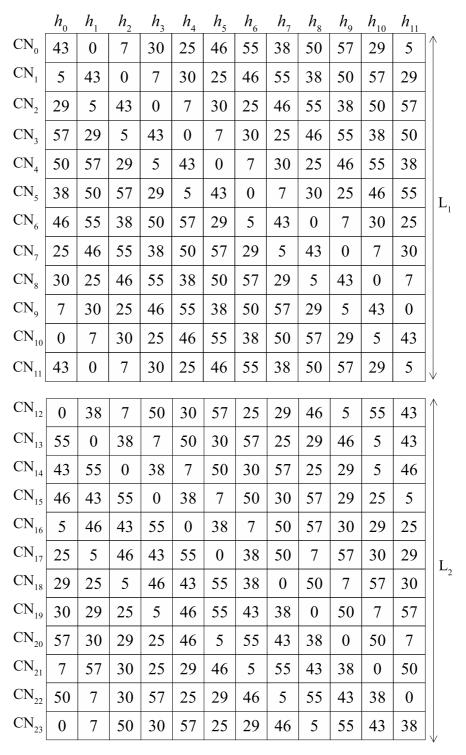

| 3.1         | Matrix representation of a S-Bubble Check FB-CN with $d_c = 12$ and $n_m = 20$ . The $b = 1680$ red circles represent the bubbles in the original FB-CN algorithm. The squares represent the remaining $b^o = 648$ bubbles after the pruning process in the S-FB algorithm |

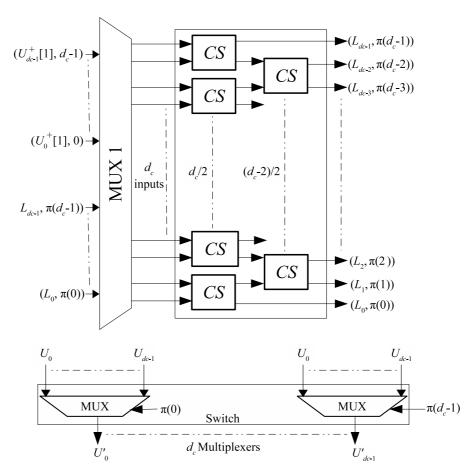

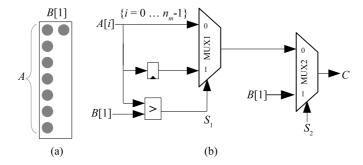

| 3.2         | Architecture of the Sorter and Switch blocks. The Sorter architecture follows [45]                                                                                                                                                                                         |

| 3.3         | S-4B architecture                                                                                                                                                                                                                                                          |

| 3.4         | S-2B architecture                                                                                                                                                                                                                                                          |

| 3.5         | S-1B+1 ECN and its architecture                                                                                                                                                                                                                                            |

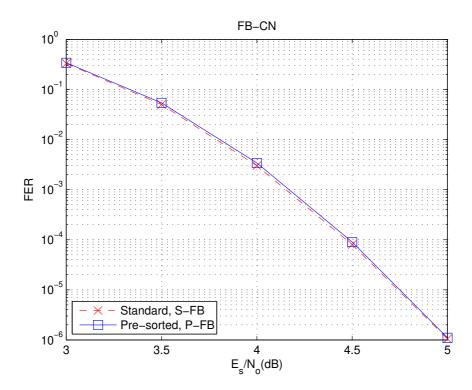

| 3.6         | Simulation results of NB-LDPC decoding algorithms for (576, 480)                                                                                                                                                                                                           |

| 2 7         | code over GF(64) and $d_c = 12$ under AWGN channel                                                                                                                                                                                                                         |

| 3.7         | EF CN Architecture                                                                                                                                                                                                                                                         |

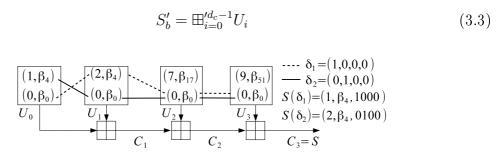

| 3.8         | Example to illustrate the redundant syndromes                                                                                                                                                                                                                              |

14 list of figures

| 3.9          | Architecture of the proposed PS EF CN with $d_c = 12$ , $n_b \le 4$ ( $n_{m,in} =$                                            |     |

|--------------|-------------------------------------------------------------------------------------------------------------------------------|-----|

|              | 5), $n_c^{12} = n_s = 20$ , where $n_c^{12}$ is the number of output bubbles of S-5B.                                         | 43  |

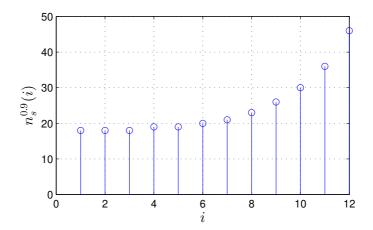

| 3.10         | Maximum number of syndromes needed to be generated, for each out-                                                             |     |

|              | put $V_i'$ , $n_{op} = 18$ valid syndromes. The output number is denoted by                                                   |     |

|              | i. The code rate is $R = 5/6$ and $E_b/N_0 = 4.5$ dB                                                                          | 45  |

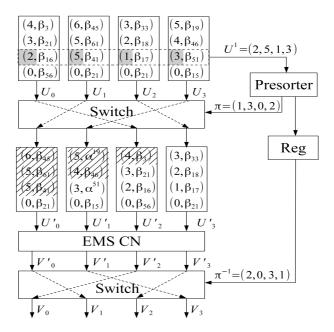

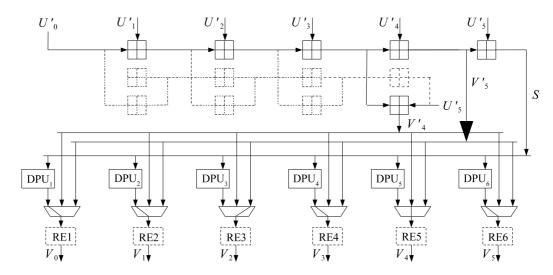

| 3.11         | $HB(0, 4, 2)$ architecture for a CN with $d_c = 6$ . The last two outputs                                                     |     |

|              | $V_3'$ and $V_4'$ are generated by a classical FB architecture                                                                | 45  |

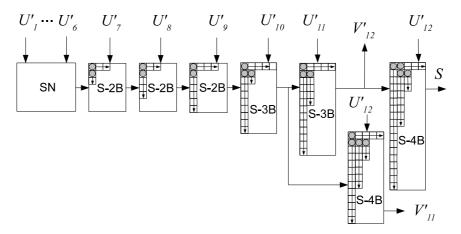

| 3.12         | $HB(6, 4, 2)$ architecture with $d_c = 12$ , $n_{m,out} = 16$ , $n_{m,in} = 5$ and                                            |     |

|              | $n_s = 20.\dots$                                                                                                              | 46  |

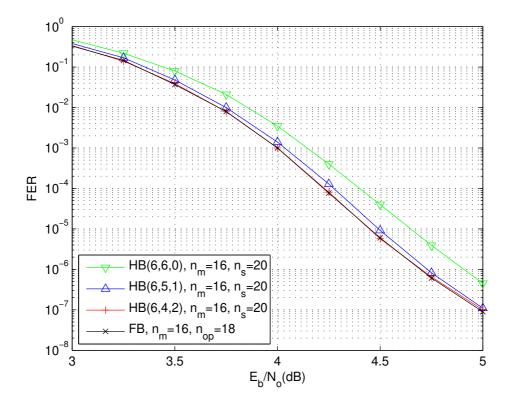

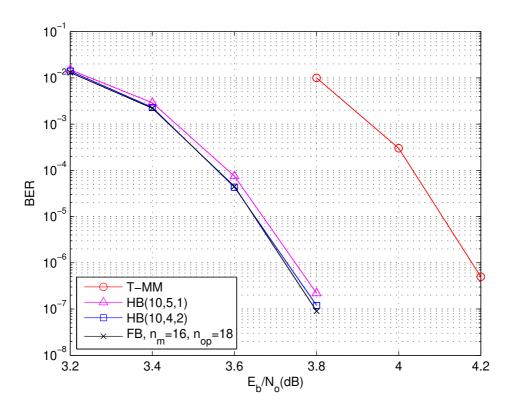

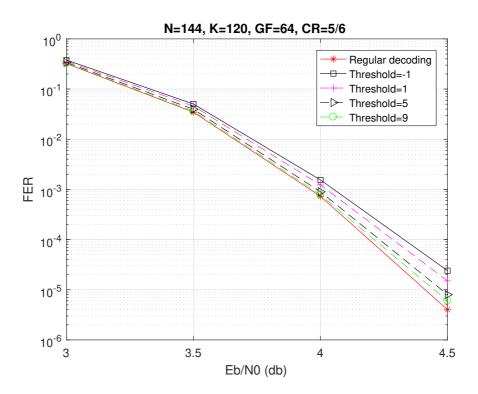

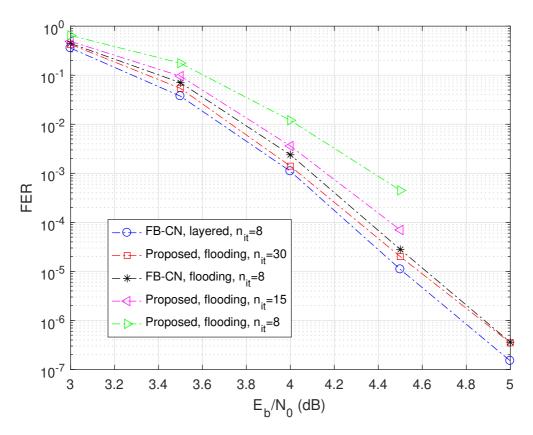

| 3.13         | FER performance for a (144, 120) NB-LDPC code over GF(64)                                                                     | 48  |

| 3.14         | FER performance for a (144, 120) NB-LDPC code over GF(256)                                                                    | 49  |

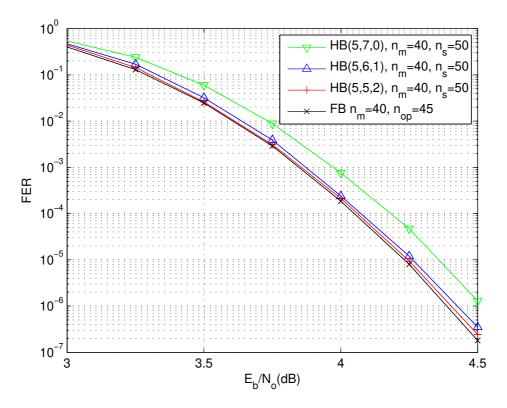

| 3.15         | BER performance for a (1536, 1344) NB-LDPC code over GF(64).                                                                  | 50  |

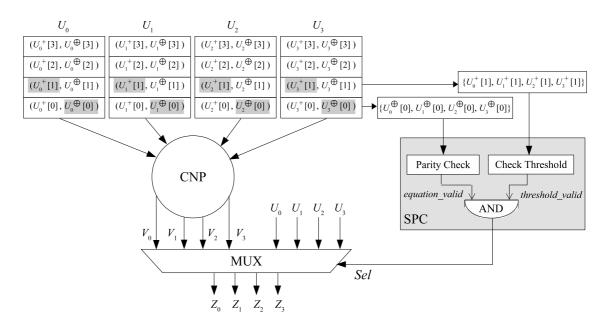

| 3.16         | CN with SPC                                                                                                                   | 53  |

| 3.17         | Simulation results in case of CR=5/6                                                                                          | 54  |

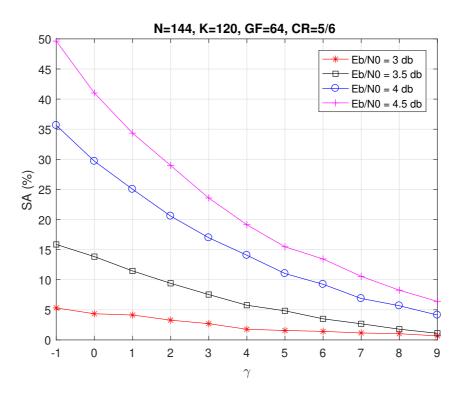

| 3.18         | Saving in % of not making a CN for CR=5/6                                                                                     | 55  |

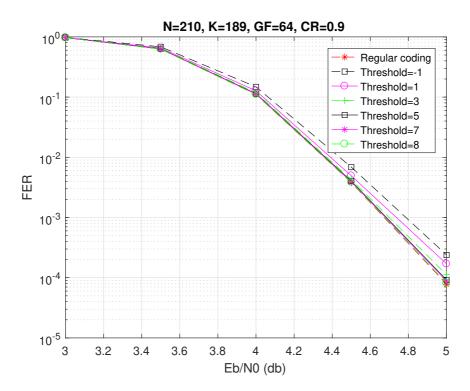

| 3.19         | Simulation results in case of CR=9/10                                                                                         | 56  |

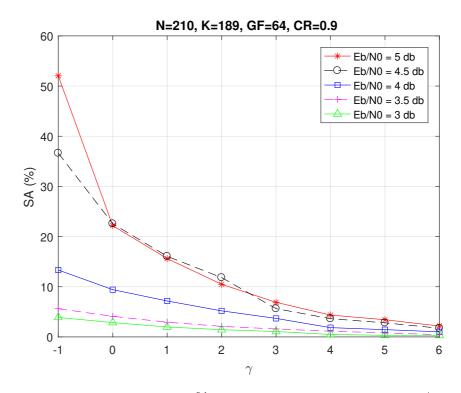

| 3.20         | Saving in % of not making a CN for CR=3/4                                                                                     | 57  |

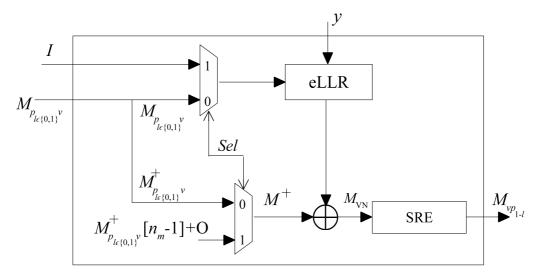

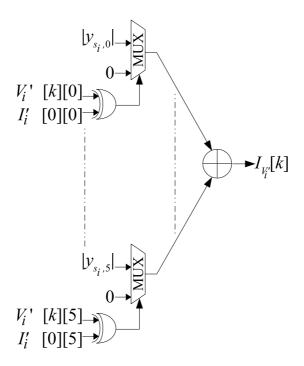

| 3.21         | Proposed architecture of the VN update mode                                                                                   | 57  |

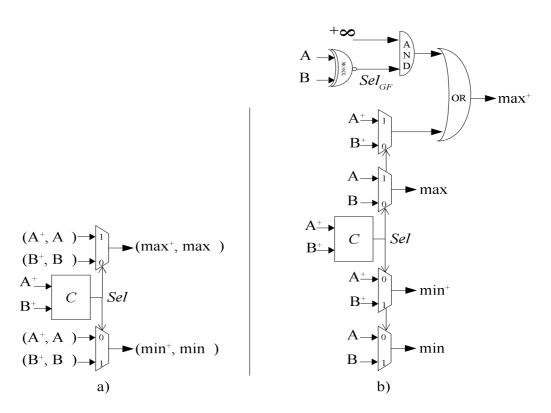

| 3.22         | Architectures of the classical and the modified comparator-swap                                                               | 58  |

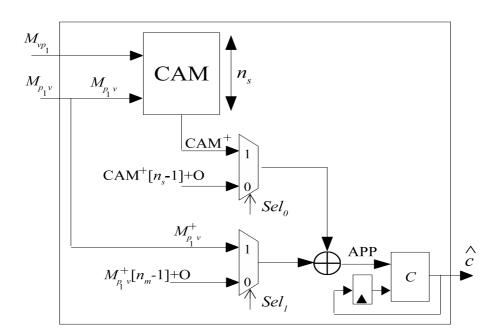

| 3.23         | Architecture of the proposed VN decision-making mode                                                                          | 59  |

|              |                                                                                                                               |     |

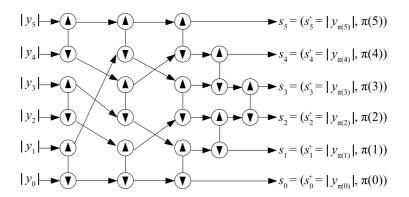

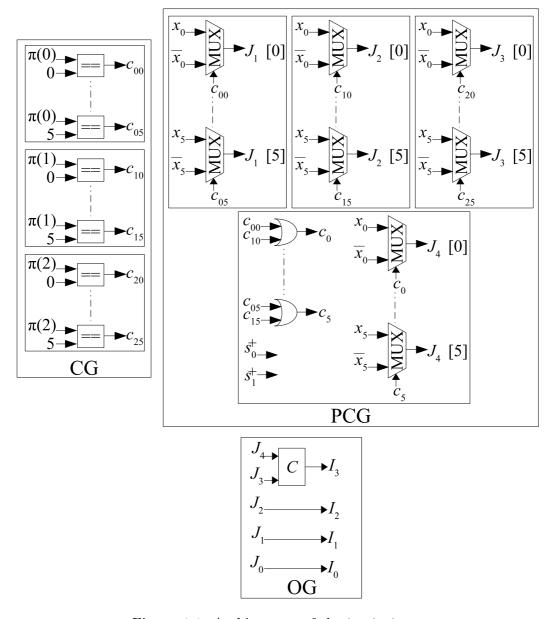

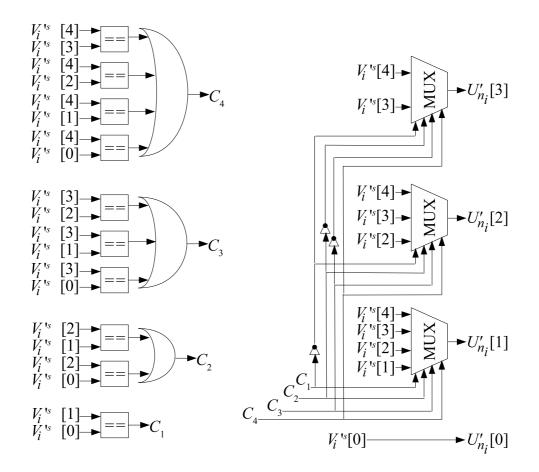

| 4.1          | Sorter architecture of the observed bits                                                                                      | 66  |

| 4.2          | Sorter Architecture generating the most reliable $n_m$ intrinsic LLRs,                                                        |     |

|              | $n_m = 12. \dots \dots$ | 68  |

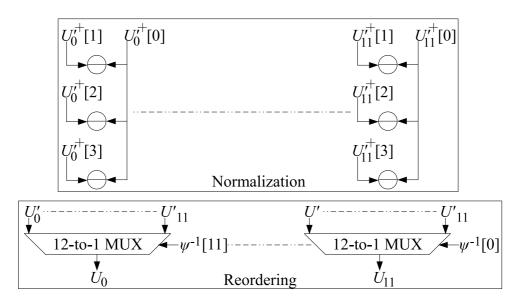

| 4.3          | Sorter architecture of the observed bits                                                                                      | 70  |

| 4.4          | Architecture of the intrinsic outputs                                                                                         | 71  |

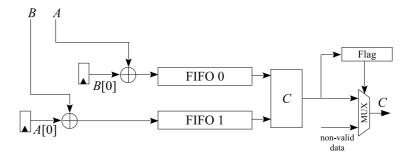

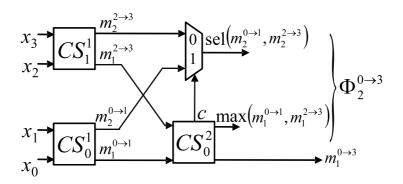

| 4.5          | ESU (4-SU) Architecture                                                                                                       | 72  |

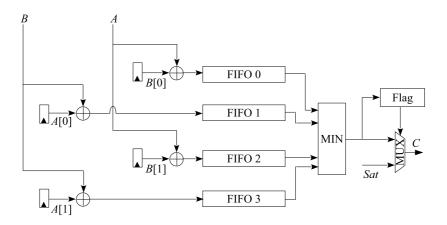

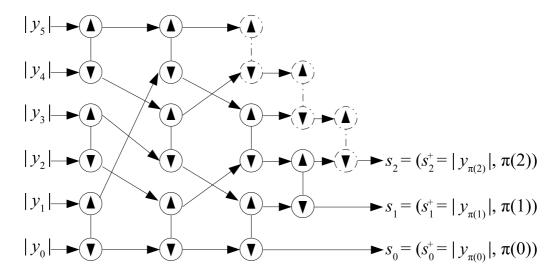

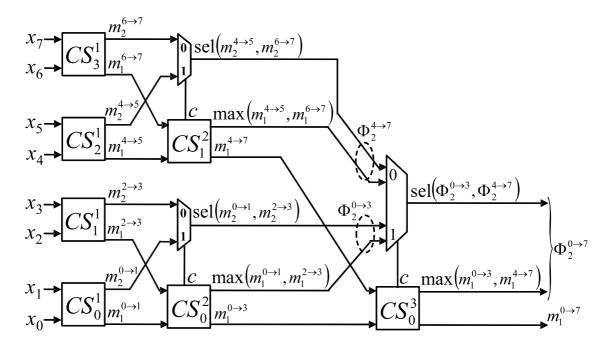

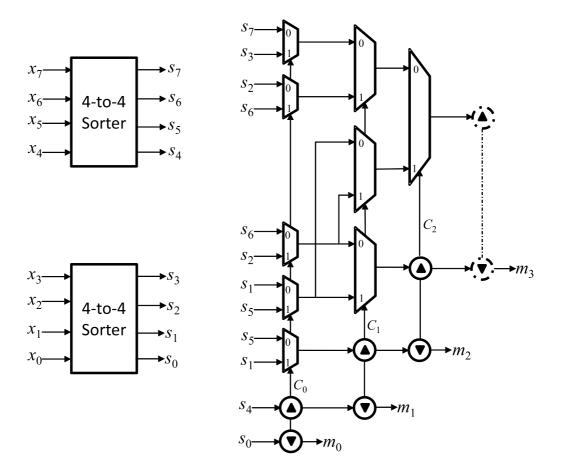

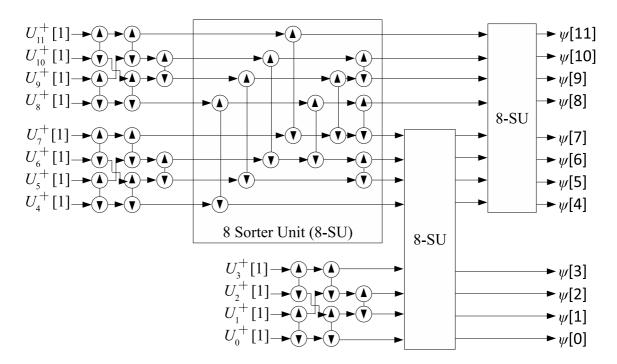

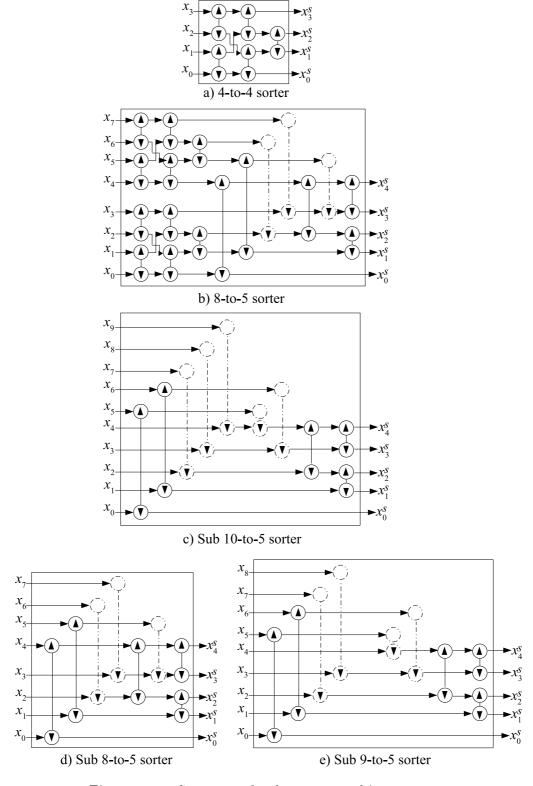

| 4.6          | 8-SU Architecture                                                                                                             | 74  |

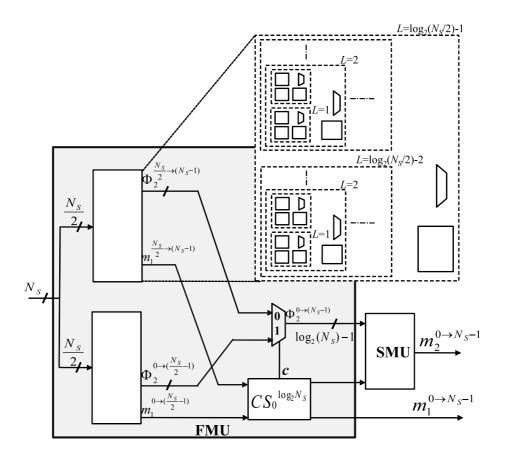

| 4.7          | $N_s$ -SU Architecture, $N_s = 2^k$                                                                                           | 76  |

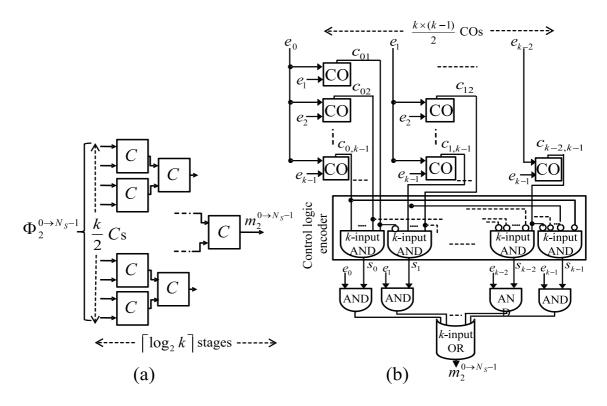

| 4.8          | SMU Architectures for $N_s$ -SU, $N_s = 2^k$ : (a) SMU-TS (b) SMU-PS .                                                        | 77  |

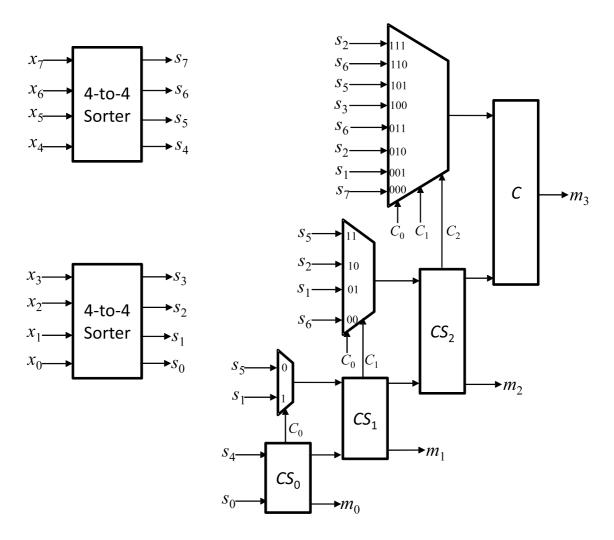

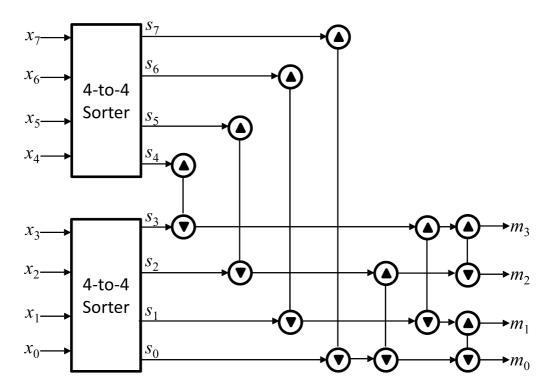

| 4.9          | Proposed 8-to-4 sorter architecture                                                                                           | 81  |

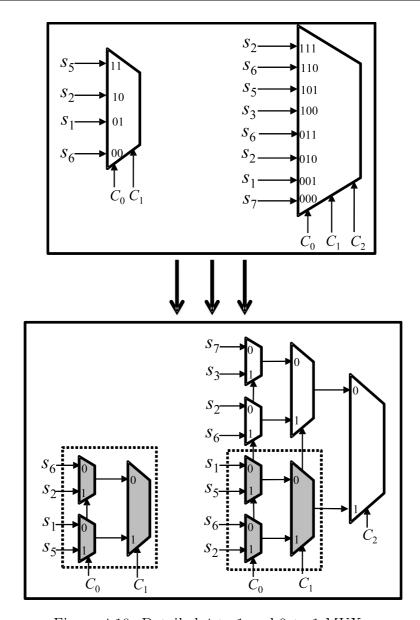

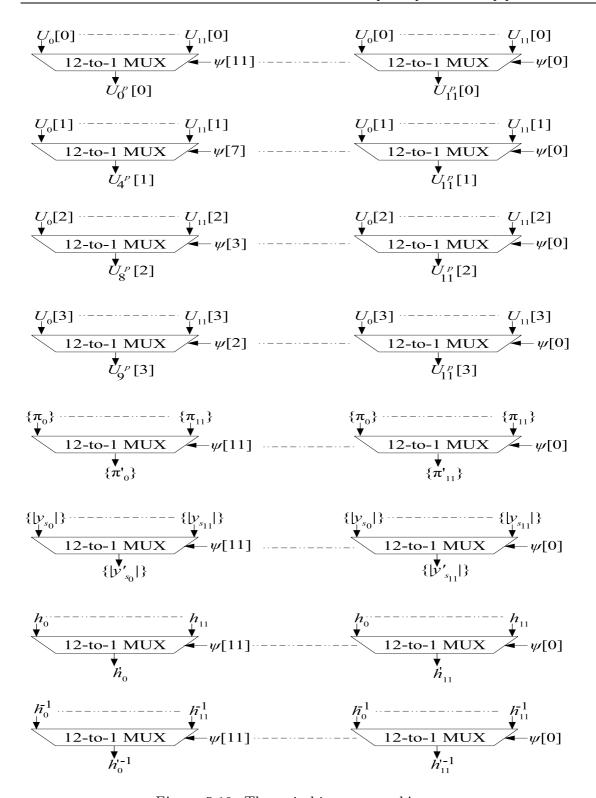

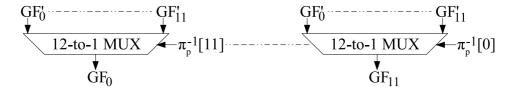

| 4.10         | Detailed 4-to-1 and 8-to-1 MUXs                                                                                               | 82  |

| 4.11         | Architecture of the simplified proposed 8-to-4 sorter                                                                         | 83  |

| 4.12         | Architecture of the odd-even 8-to-4 sorter                                                                                    | 84  |

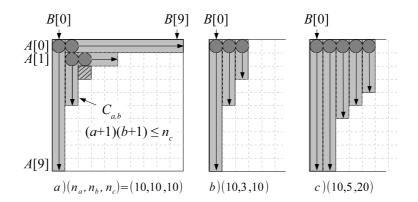

| 5.1          | The Tanalagy of PCM                                                                                                           | 86  |

| 5.1 - 5.2    | The Topology of PCM                                                                                                           | 87  |

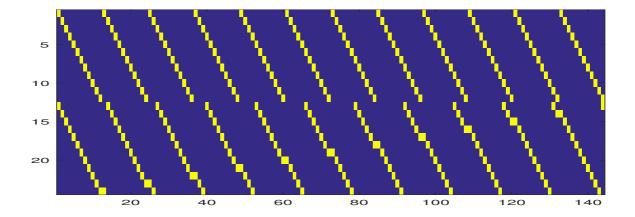

| 5.2<br>5.3   | The non-zero coefficients of the PCM                                                                                          | 89  |

|              |                                                                                                                               |     |

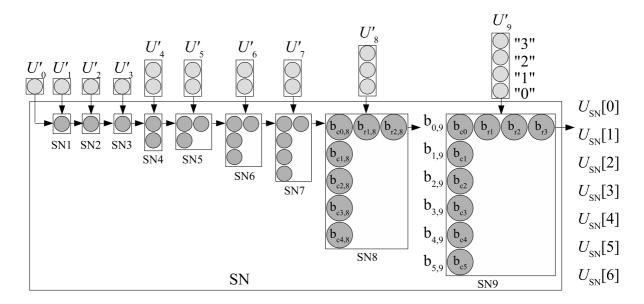

| $5.4 \\ 5.5$ | SN shape.                                                                                                                     | 90  |

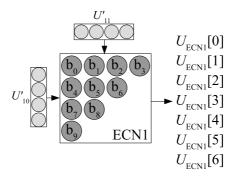

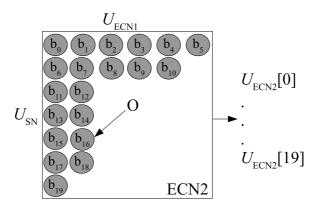

|              | ECN2 shape                                                                                                                    | 93  |

| 5.6          | ECN2 and ECN4 atwestures                                                                                                      | 94  |

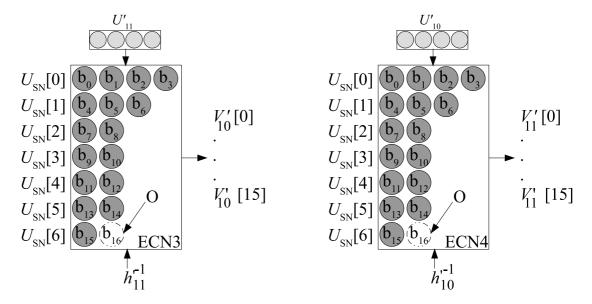

| 5.7          | ECN3 and ECN4 structures                                                                                                      | 95  |

| 5.8          | FER performance for a (144, 120) NB-LDPC code: Proposed decoder                                                               | 0.0 |

|              | vs FB CN-based decoder                                                                                                        | 98  |

list of figures 15

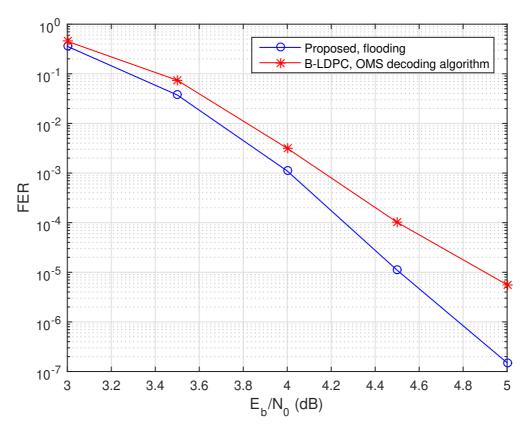

| 5.9  | FER performance for a (144, 120) NB-LDPC code over GF(64) Pro-        |

|------|-----------------------------------------------------------------------|

|      | posed decoder vs (864, 720) B-LDPC code over GF(2) OMS decoder.       |

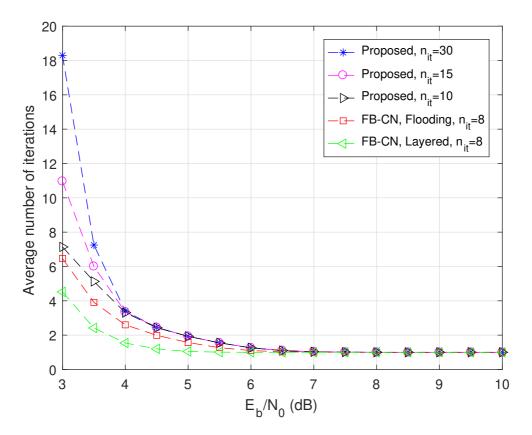

| 5.10 | Average number of iterations versus $E_b/N_0$                         |

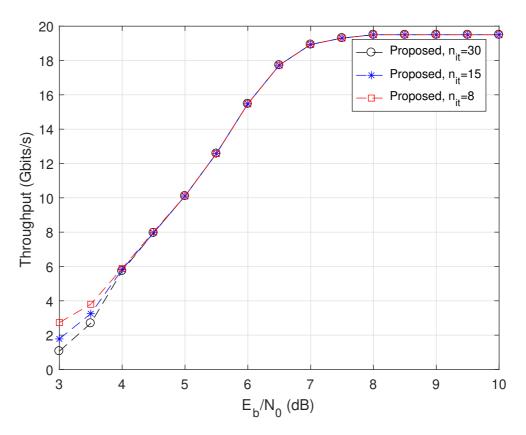

| 5.11 | Throughput versus $E_b/N_0$                                           |

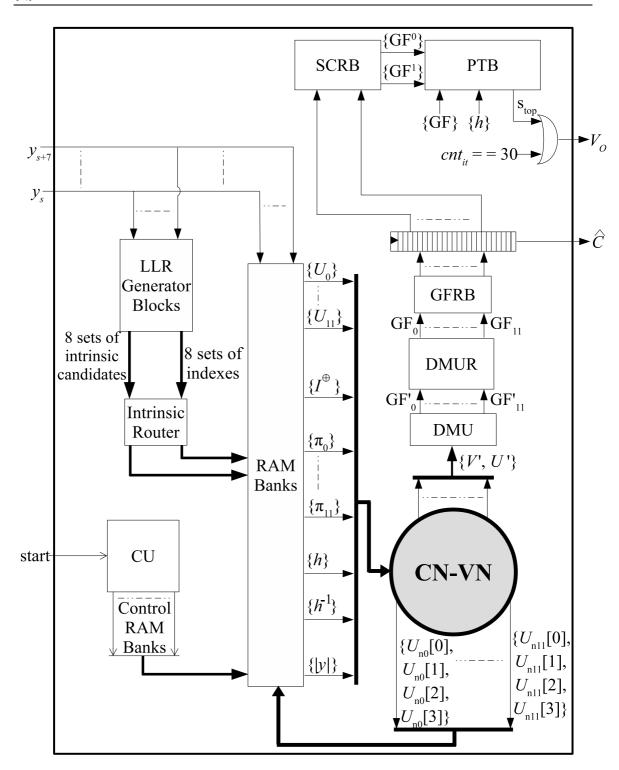

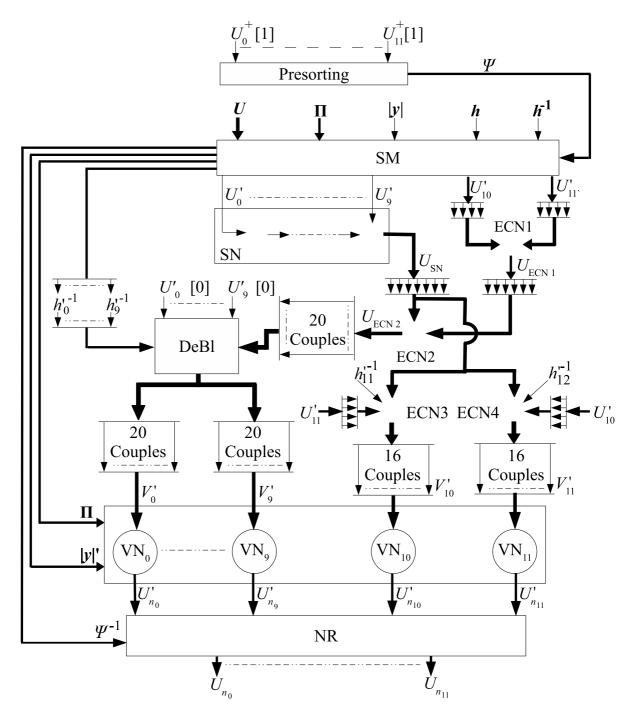

| 5.12 | Global architecture of the decoder                                    |

| 5.13 | 12 intrinsic RAMs                                                     |

| 5.14 | Extrinsic RAMs                                                        |

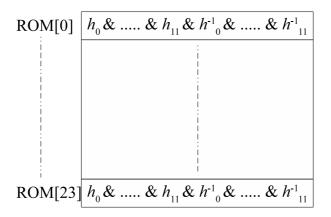

| 5.15 | ROM block                                                             |

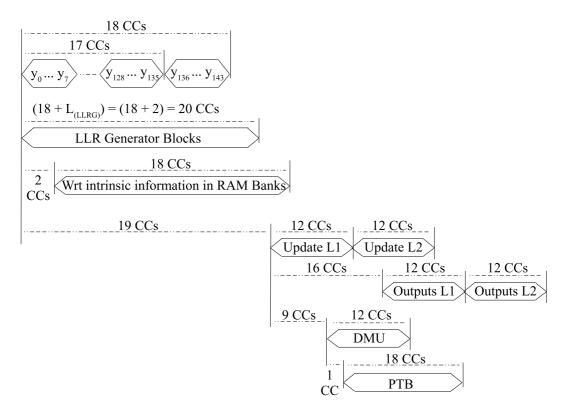

| 5.16 | Timing diagram of the overall decoder                                 |

| 5.17 | Architecture of the CN-VN unit                                        |

| 5.18 | Architecture of the presorting block                                  |

| 5.19 | The switching part architecture                                       |

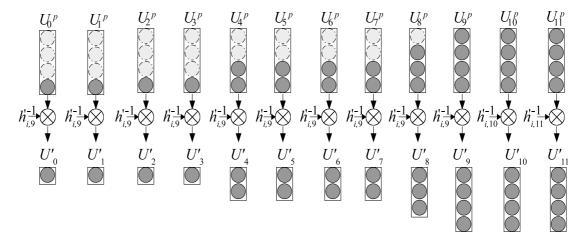

| 5.20 | The multiplication part architecture                                  |

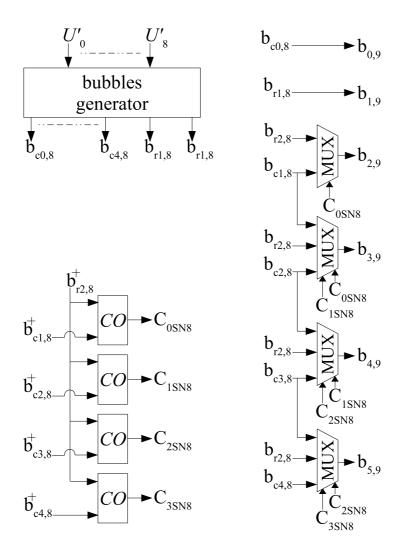

| 5.21 | The bubbles of SN8                                                    |

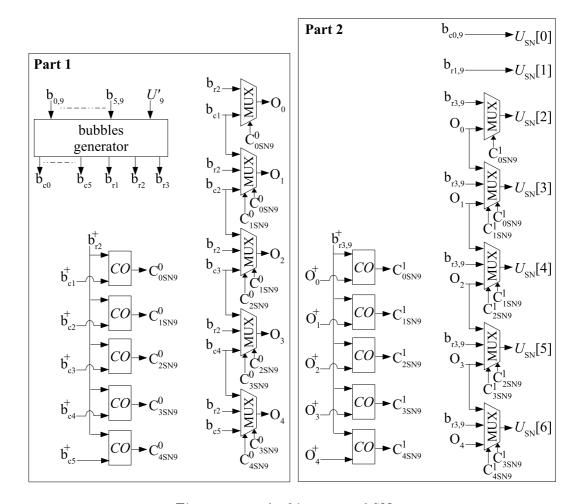

| 5.22 | Architecture of the merged SN1 to SN8                                 |

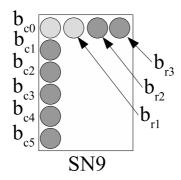

| 5.23 | The bubbles of SN9                                                    |

| 5.24 | Architecture of SN9                                                   |

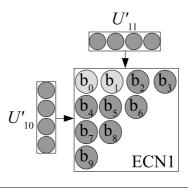

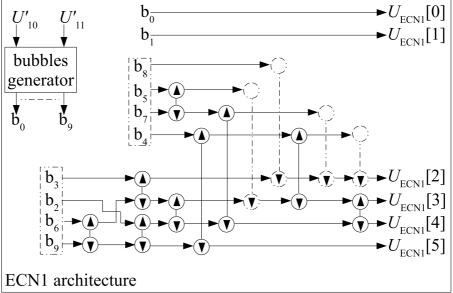

| 5.25 | The shape and the architecture of ECN1                                |

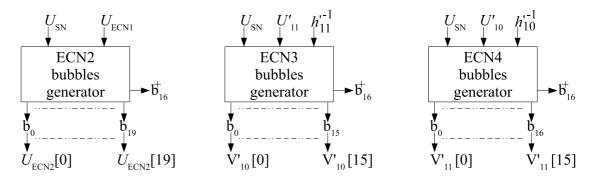

| 5.26 | bubbles generator of ECN2, ECN3 and ECN4                              |

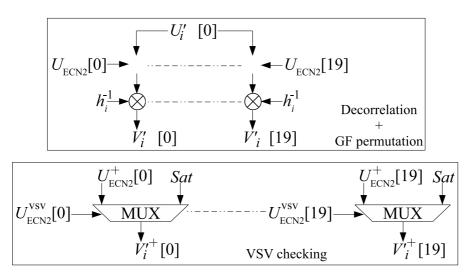

| 5.27 | DeBl Architecture                                                     |

| 5.28 | VN architecture                                                       |

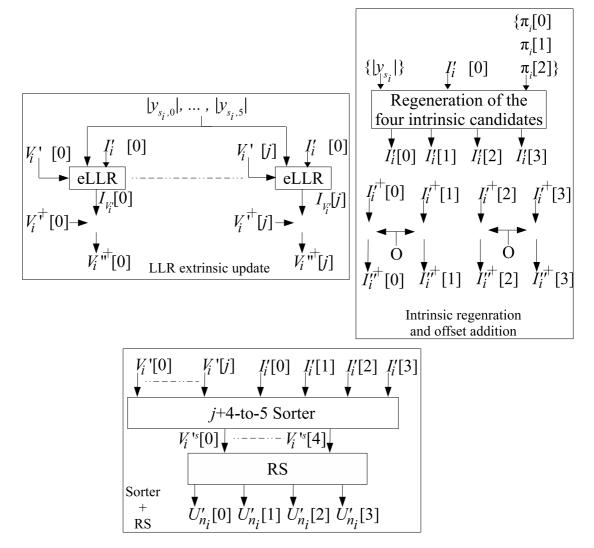

| 5.29 | eLLR architecture                                                     |

| 5.30 | 24-to-5 architecture                                                  |

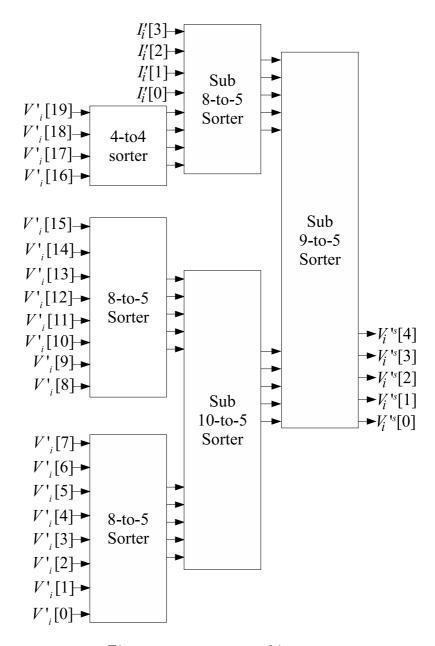

| 5.31 | Sorters and sub-sorters architectures                                 |

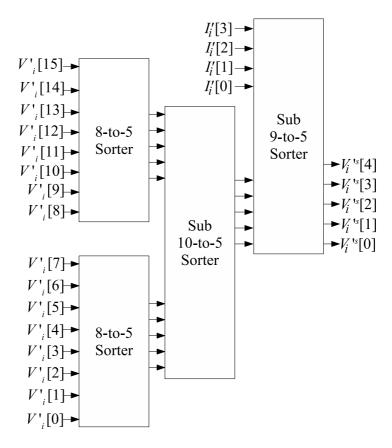

| 5.32 | 20-to-5 architecture                                                  |

| 5.33 | Architecture of the redundant suppression block                       |

| 5.34 | NR architecture                                                       |

| 5.35 | Timing diagram of the CN-VN unit                                      |

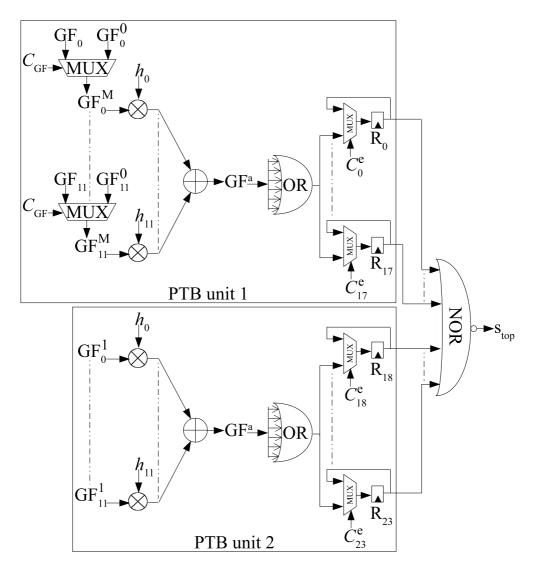

| 5.36 | DMU Architecture                                                      |

| 5.37 | DMUR architecture                                                     |

| 5.38 | Timing diagram of the DMU unit                                        |

| 5.39 | SD architecture                                                       |

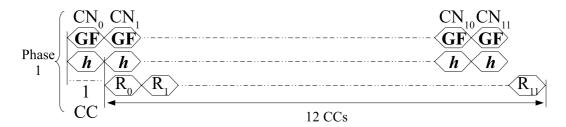

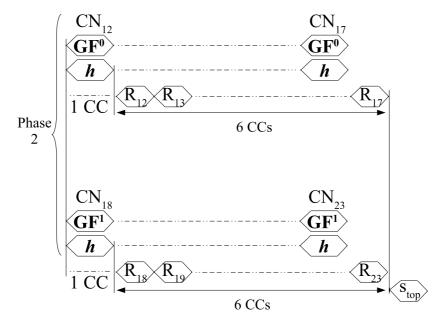

| 5.40 | Timing diagram of PTB phase 1                                         |

| 5.41 | Timing diagram of PTB phase 2                                         |

| 5.42 | Timing diagram of the decoder in case of processing two frames simul- |

|      | taneously                                                             |

| 5.43 | Timing diagram of the decoder in case of interleaving frames 1        |

| 5.44 | Overall hardware emulation architecture                               |

| 5.45 | Symbol generator architecture                                         |

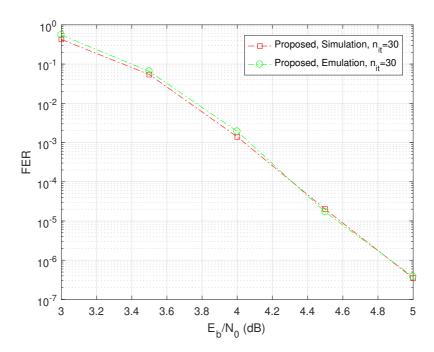

| 5.46 | Simulation and emulation results of NB-LDPC decoding algorithms       |

| -    | for (864, 720) code over GF(64) and $d_c = 12$ under AWGN channel     |

|      | (FER versus $E_b/N_0$ )                                               |

|      | ` ' ',                                                                |

16 list of figures

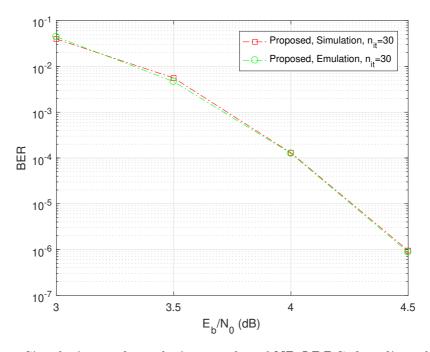

| 5.47 | Simulation and emulation results of NB-LDPC decoding algorithms for |     |

|------|---------------------------------------------------------------------|-----|

|      | (864, 720) code over GF(64) and $d_c = 12$ under AWGN channel (BER  |     |

|      | versus $E_b/N_0$ )                                                  | 136 |

# List of Tables

| 3.1<br>3.2 | Number of ECN schemes for different $d_c$ values                                                          | 38      |

|------------|-----------------------------------------------------------------------------------------------------------|---------|

|            | FPGA                                                                                                      | 39      |

| 3.3        | Post-synthesis results for the FB-CNs with (P-FB) and without (S-FB) pre-sorting on a Xilinx FPGA device. | 39      |

| 3.4        | Post-synthesis results for different ECN architectures and CN sub-<br>units on 28 nm FD-SOI technology    | 51      |

| 3.5        | Post-synthesis results for CN architectures on 28 nm FD-SOI technology.                                   | $5^{1}$ |

| 3.6        | Area and energy efficiency for different architectures                                                    | 52      |

| 3.7        | HB and SB comparison                                                                                      | 53      |

| 3.8        | Complexity analysis of the VNP using Xilinx Virtex6, xc6vlx240t-                                          |         |

|            | 2ff1156 device                                                                                            | 60      |

| 4.1        | The elements of $\Phi_{n_{\pi}=16}$                                                                       | 67      |

| 4.2        | Synthesis results on virtex 6, xc6vlx240t -2 ff1156 FPGA device                                           | 69      |

| 4.3        | Computational Complexity Comparison                                                                       | 78      |

| 4.4        | Post-synthesis results of $N_s$ -SU on TSMC 28 $nm$ , Non-Pipelined Ar-                                   |         |

|            | chitecture (A: Area, C: Critical Path, P: Power)                                                          | 79      |

| 4.5        | Post-synthesis results of $N_s$ -SU on TSMC 28 $nm$ , Pipelined Architec-                                 |         |

|            | ture (A: Area, C: Critical Path, P: Power)                                                                | 79      |

| 5.1        | COMPARISON OF STATE-OF-THE-ART NB-LDPC DECODERS                                                           |         |

|            | (ASICs)                                                                                                   | 132     |

| 5.2        |                                                                                                           | 133     |

| 6.1        | Example of messages used for T-EMS                                                                        | 141     |

| 6.2        | -                                                                                                         | 141     |

| TA.1       | Conventional rules of both multiplicative and additive notations                                          | 145     |

|            | <del>-</del>                                                                                              | 146     |

| TA.3       | modulo 2 multiplication                                                                                   | 146     |

### Acronyms

A Area

AE Area Efficiency

AER Area Efficiency Ratio

APP A Posteriori Probability

ASIC Application-Specific Integrated Circuit

AWGN Additive White Gaussian Noise

BER Bit Error Rate

BP Belief Propagation

BPSK Binary Phase-Shift Keying

$\mathbb{C}$  Set of complex numbers

C Critical Path

CO Comparator Only

C Comparator

CS Comparator Swap

CL Cycle Latency

CG Control Generator

CC Clock Cycle

CU Control Unit

CAM Content Addressable Memory

CN Check Node

CNP Check Node Processor

CR code rate equal to  $\frac{K}{N} = 1 - \frac{d_v}{d_c}$

DBV Discard Binary Vector

DU Decorrelation Unit

DPU Decorrelation Processor Unit

DMU Decision Making Unit

DMUR DMU Reordering

DeBl Decorrelation + Devision Block

DMUS DMU Storage

DAVINCI Design And Versatile Implementation of Non-binary wireless

Communications based on Innovative LDPC codes

DVB Digital Video Broadcast

EF-CN Extended Forward Check Node

EE Energy Efficiency

ESU Elementary Sorting Unit EMB Encoded Modulated Bits

ES Extrinsic Storage

ECN Elementary Check Node

EMS Extended Min-Sum

FB-CN Forward Backward Check Node

FTSES First then Second Extrema Selection

FER Frame Error Rate

FMU First Minimum Unit

FPHD Fully Parallel Hybrid Decoder

FFT Fast Fourier Transform

FIFO First-In First-Out

Gel/s Gega elements per second

GFRB GF Routing Block

GF Galois Field

H-CN Hybrid Check NodeH Parity Check MatrixHEP High Energy Efficiency

HD Hard Decision

I Intrinsic messages

IL-MwBRB Improved Layered Multiple-symbol-reliability

weighted Bit-Reliability Based

IW Input WrapperIS Intrinsic Storage

IFFT Inverse Fast Fourier Transform

LDPC Low Density Parity Check

LLR Log Likelihood Ratio

Lab-STICC Laboratoire des Sciences et Techniques de l'Information

de la Communication et de la Connaissance

LDPC Low-Density Parity-Check

LLR Log-Likelihood Ratio

LUT Look Up Table

MS Min Sum

NB Non Binary

NB-LDPC Non-Binary LDPC

NR Normalization + Reordering

O.S Occupied Slices

OG Outputs Generator

OMS Offset Min Sum OW Output Wrapper

P-FB FB-CN with Presorting

P Power

$P_{clk}$  Clock Period

PCG Possible Candidates Generator

PS Parallel Structure

PE Power Efficiency

PER Power Efficiency Ratio

PTB Parity Test Block

PCM Parity Check Matrix

QC-LDPC Quasi Cyclic LDPC  $\mathbb{R}$  Set of real numbers

RE Redundant Elimination

RTL Register Transfer Level

RS Redundant Suppression

RAM Random Access Memory

ROM Read Only Memory

SB-CN Syndrome Based Check Node

S-FB FB-CN without Presorting

SPC Skip Processing Controller

SN Syndrome Node SA Saving Amount

SRE Sorter + Redundant Elimination

SU Sorting Unit

SMU Second Minimum Unit

SCRB Stopping Criteria Router Block

SM Switching + Multiplication

T-MM Trellis Min Max

TS Tree Structure

TEC Throughput Error Computation

VN Variable Node

VNP Variable Node Processor

VHDL VHSIC Hardware Description Language

$\mathbb{N}$  Set of natural integers  $\mathbb{Z}$  Set of relative integers

WIFI Wireless Local Area Network

WIMAX Worldwide Interoperability for Microwave Access

#### **Parameters**

q Order of GF

m Number of bits to represent a GF value

$n_m$  Number of considered GF elements among q GF elements

$n_{iter}$  Number of maximum iterations

$M^+$  LLR value of M GF value of M

$d_c$  Degree of the CN (number of VNs connected to a CN)  $d_v$  Degree of the VN (number of CNs connected to a VN)

K number of information symbols M number of redundant symbols N = K + M code length (number of VNs)

$h_{i,j}$  Non-zero value in PCM that connects  $CN_i$  with  $VN_j$

$M_{v_j p_i}$  Messages sent from  $VN_j$  to  $CN_i$  $M_{p_i v_j}$  Messages sent from  $CN_i$  to  $VN_j$

$d_v$  Degree of the variable node (number of CNs connected to a VN)  $d_c$  Degree of the check node (number of VNs connected to a CN)

# Chapter 1

### Introduction

The thesis is a part of a collaborative framework between the Université Bretagne Sud (UBS, France) and the Lebanese University (LU, Lebanon) and has been supervised by Prof. Emmanuel Boutillon, Prof. Ali Alaeddine, Dr. Ali Al Ghouwayel and Dr. Laura Conde-Canencia. During these years I also collaborated with Dr. Cédric Marchand who provided significant inputs for my work.

In 1948, Shannon showed that reliable communications are possible thanks to error control coding [5]. Since then, numerous error-correcting schemes have been proposed including algebraic and convolutional codes. With the invention of Turbo codes in the early 90s [12], followed by the rediscovery of LDPC [15, 16], iterative decoding algorithms based on trellises or graphs became a main topic of study. Recently, other decoding approaches have been proposed (e.g. with the introduction of Polar codes). Today, error-correcting codes are ubiquitous and adopted in almost every modern digital communication system for wireless communications, sensor networks and deepspace communications, among others. New-generation standards and other emerging applications demand codes with near-optimal error-correcting capabilities. However, the design and implementation of those high-performance error-correcting codes also face many challenges that include low energy consumption, high throughput and low implementation area.

Even if most of the standardized coding schemes are binary, non-binary LDPC codes have been proven to outperform convolutional Turbo codes and binary LDPC codes. In fact, this new family of codes retains the benefits of steep waterfall region for short codewords (typical of Turbo codes) and low error floor (typical of binary LDPC). Another advantage of non-binary LDPC codes is that, compared to binary LDPC, they generally present higher girths, which leads to better decoding performance. Moreover, since non-binary LDPC codes are defined on high-order fields, there is a closer connection between non-binary LDPC and high-order modulation schemes. However,

2 Introduction

the main drawback of non-binary LDPC codes is their increased decoding complexity.

The work presented in this report deals with the study of new non-binary LDPC decoding algorithms for high order fields ( $q \geq 64$ ) and their associated architectures. We aim at reducing the hardware complexity and/or increase the area and throughput efficiency. We mainly focus on the Extended Min Sum (EMS) decoding algorithm because of its competitive error-correcting performance. During this PhD we have mainly considered the three following goals: first, the reduction of the decoder cost by eliminating the inner elements not relevant in the output generation. This first goal implies the sorting of the input list, thus, the second goal has been the design of an efficient architecture for this sorting task. The third and final goal was the implementation of a highly parallel decoder for non-binary LDPC codes.

So far, the results obtained through this PhD have been spread in the scientific community through the following publications:

Cédric Marchand, Emmanuel Boutillon, Hassan Harb, Laura Conde-Canencia, Ali Al Ghouwayel, "Extended-Forward Architecture for Simplified Check Node Processing in NB-LDPC Decoders", IEEE International Workshop on Signal Processing Systems (SIPS'2017), Dallas, United States. Oct. 2016.

Hassan Harb, Cédric Marchand, Laura Conde-Canencia, Emmanuel Boutillon, Ali Al Ghouwayel, "Pre-sorted Forward-Backward NB-LDPC Check Node Architecture", IEEE International Workshop on Signal Processing Systems (SIPS'2016), Lorient, France, Oct. 2017.

Titouan Gendron, Hassan Harb, Alban Derrien, Cédric Marchand, Laura Conde-Canencia, Bertand Le Gal and Emmanuel Boutillon, "Demo: Construction of good Non-Binary Low Density Parity Check codes", Demo night at SIPS'2017, Lorient, France, Oct. 2017.

Hassan Harb, Emmanuel Boutillon, Bertrand Le Gal, "Real-time evaluation of NB-LDPC codes thanks to HLS-based hardware emulation", Demo night at DASIP'2018, Porto, Portugal, Oct. 2018.

Cédric Marchand, Emmanuel Boutillon, Hassan Harb, Laura Conde-Canencia and Ali Al Ghouwayel, "Hybrid Check Node Architectures for NB-LDPC Decoders", Accepted in IEEE Transactions on Circuits And Systems-I, August 2018.

Therefore, this manuscript is organized as follows:

Chapter 2: This chapter introduces LDPC codes as well as the main decoding algorithms and their associated architectures. Section 1 presents notation and definitions related to binary and NB-LDPC codes. Section 2 de-

scribes several decoding algorithms such as the Belief-Propagation and the Min-Max. Section 3 and 4 show some of the existing serial CN and VN architectures respectively. Section 4 reviews processing schedules that are considered in most of the literature. Finally, Section 6 highlights some of the state-of-the-art high-throughput decoding architectures.

- Chapter 3: This chapter presents my different contributions to improve the existing NB-LDPC decoder architectures. These contributions are detailed at the different blocks of the decoder. Section 1 shows the modifications on the CN processor block and Section 2 presents the modifications on the VN processor block.

- Chapter 4: This chapter is dedicated to parallel pipelined architectures providing higher throughput and better hardware efficiency than the serial ones. Section 1 shows a new technique to implement the LLR generator that is included in most of the NB-LDPC decoder algorithms. Then, section 2 presents the proposed parallel pipelined sorter algorithm along with an example of its extended approach.

- Chapter 5: The proposed high-throughput fully-parallel pipelined NB-LDPC decoder architecture is shown in this chapter. Section 1 introduces the considered NB-LDPC code along with the decoding algorithm and the simulation results. Section 2 shows the global decoder architecture where the parallelism of the exchanged data is presented along with the memorization system and the timing diagram. Section 3 presents in details the architecture of each block. Section 4 shows the timing diagram of the global processing of the decoder where the frame interleaving is demonstrated. The chapter continues with section 5 where the synthesis analysis is shown. Finally, section 6 shows the global architecture of the hardware emulation.

**Chapter 6:** This chapter concludes the work and presents our perspectives.

Finally, it is worth mentioning that not all the work done in the 3 years period of my PhD has been included in this document. I have decided to focus only on hardware implementation. Thus, concerning NB-LDPC matrix construction, in a few words, I have contributed to the generation of the Lab-STICC NB-LDPC database<sup>(1)</sup> by writing a gecode program<sup>(2)</sup> (a constraint programming Frame work) that optimizes both the girth of the matrix and the affectation of GF coefficients on non-nul positions (see [56]). Recently, I also proposed a new NB-LDPC structure that allows, thanks to a trick, to use a NB-LDPC decoder of a certain rate to decode NB-LDPC codes of higher rate, opening thus the path toward hardware flexibility.

$<sup>^{(1)}</sup>$ http://www-labsticc.univ-ubs.fr/nb | ldpc/MatricesDir/toto.html

<sup>(2)</sup> www.gecode.org

# Chapter 2

# NB-LDPC codes: Principles, Decoding Algorithms and Architectures

This chapter first introduces NB-LDPC codes. Then, two state-of-the-art check node algorithms are recalled and two different schedules of decoding process (Layered and Flooding) are described. Finally, some of the NB-LDPC state-of-the-art decoding architectures are presented. (Section 2.1 and most of Section 2.2 are derived from [7]). For mathematical background about the GF definition and construction, the reader is referred to Appendix A.

#### 2.1 Non-Binary LDPC codes defined on a Galois field

An LDPC code is a linear block code defined by a sparse Parity Check Matrix (PCM), denoted by H, of dimensions  $M \times N$  designed over GF(q=2). This code is binary since its symbols belong to  $GF(2) = \{0,1\}$ . The number of rows, M, corresponds to the number of parity check constraints of the code. The number of columns, N, corresponds to the length of the codewords. A codeword consists of K information symbols and M = N - K redundancy symbols added by the encoder. The parity check constraints of H must be respected by the codewords in the construction. Thus, a message C of length N is a codeword if and only if  $C.H^T=0$ , where  $H^T$  is the transposed matrix of H.

Let us consider the following example of a PCM with M=4 and N=6:

$$H = \begin{bmatrix} h_{0,0} & h_{0,1} & h_{0,2} & 0 & 0 & 0 \\ 0 & h_{1,1} & 0 & h_{1,3} & h_{1,4} & 0 \\ h_{2,0} & 0 & 0 & h_{2,3} & 0 & h_{2,5} \\ 0 & 0 & h_{3,2} & 0 & h_{3,4} & h_{3,5} \end{bmatrix}$$

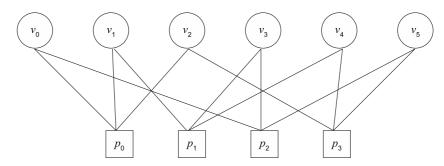

Figure 2.1: A graphic representation of an LDPC code with a bipartite graph.

A codeword  $C = [c_0, c_1, c_2, c_3, c_4, c_5]$  satisfies the four following equations:

$$h_{0,0}.c_0 + h_{0,1}.c_1 + h_{0,2}.c_2 = 0 (2.1)$$

$$h_{1,1}.c_1 + h_{1,3}.c_3 + h_{1,4}.c_4 = 0 (2.2)$$

$$h_{2,0}.c_0 + h_{2,3}.c_3 + h_{2,5}.c_5 = 0 (2.3)$$

$$h_{3,2}.c_2 + h_{3,4}.c_4 + h_{3,5}.c_5 = 0 (2.4)$$

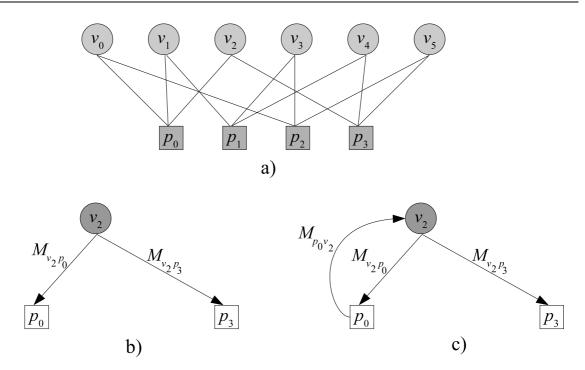

An LDPC code can also be represented by a bipartite graph (or Tanner graph) [21]. This kind of graph provides a complete description of the structure of the code and also helps to describe the decoding algorithms as will be explained in Section 2.2. A bipartite graph composed of two sets of nodes such that two nodes of the same set are connected only through one node of the other set. In the case of an LDPC code, we talk about the set of parity Check Nodes (CN) and the set of Variable Nodes (VN). A CN represents a row in the PCM (or equivalently a parity constraint) and a VN represents a column (or equivalently a symbol of the codeword). Consequently, the bipartite graph associated to an LDPC code represented by a PCM H of dimensions  $M \times N$  is composed of M CNs and N VNs. A CN  $p_i$  is related to a VN  $v_j$  if the element of the  $i^{th}$  row and  $j^{th}$  column of the PCM is non-zero (or equivalently, if the  $j^{th}$  symbol of the codeword participates in the  $i^{th}$  parity constraint). Thus, the example of the matrix H mentioned before can be represented by a Tanner graph as shown in Fig. 2.1.

The number of non-zero symbols in each column of PCM and the number of non-zero symbols in each row are respectively denoted by  $d_v$  and  $d_c$ . An LDPC code is called regular if  $d_v$  is constant for all the columns in H and  $d_c = \frac{N}{M} d_v$  is constant for all rows. Otherwise, the code is called irregular. Although irregular codes have better performance because of their highly randomized structure, regular codes are usually structured codes which makes them hardware friendly from a decoding perspective. It is possible to locate the regularity of a code using its bipartite graph. The code is regular if the number of outgoing edges of each VN and the number of outgoing edges

Figure 2.2: A graphic representation for a CN in case of NB-LDPC code [7].

of each CN are constant. Therefore,  $d_v$  and  $d_c$  are called the connectivity degrees of the VNs and CNs respectively. In the case of a regular LDPC code defined by a full rank matrix, i.e, no row of the matrix is linear combination of other rows, the code rate R of the code can be expressed as a function of  $d_v$  and  $d_c$ :

$$R = \frac{K}{N} = \frac{N - M}{N} = 1 - \frac{d_v}{d_c}.$$

(2.5)

In this manuscript, we consider the case of LDPC codes defined on Galois fields  $GF(q = 2^m)$ , m > 1, and known as NB-LDPC. Thus, the elements of the PCM matrix belong to Galois field  $GF(q = 2^m)$ , m > 1 and the matrix products of the parity equations use the internal composition laws of the Galois field. Therefore, a new class of nodes called the permutation nodes are added to the bipartite graph of Fig. 2.1 to model the multiplication of the symbols of the codeword by the non-zero elements of the PCM. Fig. 2.2 illustrates the partial bipartite graph of equation (2.2) by adding the permutation nodes that correspond to the elements  $h_{1,1}$ ,  $h_{1,3}$  and  $h_{1,4}$ .

Binary LDPC codes have asymptotic performance approaching the Shannon limit [12,13]. However, for small or medium size codewords, the performance of the binary LDPC codes degrades considerably. It is shown in [19] that this loss can be compensated by using NB-LDPC codes of high cardinality. In addition, the high cardinality of the codes ensures better resistance to packet errors [20]. However, the performance gain introduced with high Galois fields significantly increases the complexity of the decoding algorithms and their practical implementations.

Next section describes some of the state-of-the-art NB-LDPC decoding algorithms: Belief Propagation (BP) [19], Log-BP [22], Min-Sum [22], Extended Min-Sum (EMS) [24, 25] and Min-Max [27] algorithms.

#### 2.2 Iterative decoding algorithms for NB-LDPC codes

BP decoding algorithms are based on the bipartite graph defined by the NB-LDPC code. They are also called message-passing algorithms because, at each iteration, messages are transmitted from CNs to VNs and vice versa. We distinguish two types of messages:

- ▶ Intrinsic or *a priori* messages are computed from the channel observations. They are called intrinsic because the information they contain only comes from the channel. At the initialization stage, these messages are directly sent to all the CNs.

- ▶ Extrinsic messages are computed from messages coming from other branches of the graph. Outgoing extrinsic messages from a VN are computed from an intrinsic message and extrinsic messages from the connected CNs. Outgoing extrinsic messages from a CN are computed from incoming extrinsic messages (from the connected VNs) and with the local parity constraint.

The decoder should be able to converge on a valid codeword after a finite number of iterations. In practice, the decoding algorithm can be stopped according to two criteria. The simplest is to set the number of iterations independently of the convergence of the decoder. The second criterion, which permits to reduce the latency of the decoder, consists in stopping the decoding as soon as it converges to a valid codeword (an estimated codeword  $\hat{C}$  is valid if it satisfies the syndrome  $\hat{C}.H^T=0$ ). However, to avoid an infinite execution in case the decoder fails to converge to a valid codeword, a maximum number of iterations is fixed.

In the BP algorithm, the exchanged messages are a posteriori probabilities calculated on the symbols of the codeword. However, the BP algorithm [19] suffers from a prohibitive computational complexity, dominated by  $O(q^2)$ , which mainly comes from the calculations carried out during the update of the parity constraints.

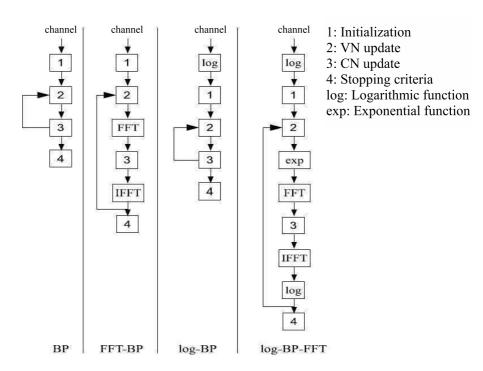

Barnault et al. proposed in [21] the FFT-BP algorithm in which the updates of the parity constraints are made in the frequency domain. This transforms the convolution products into simple multiplications. Thus, additional operations of Fourier transform, direct and inverse, are added between the VNs and the CNs to ensure the transition from the probability domain to the frequency domain, and vice versa. Although the complexity of the FFT-BP algorithm is considerably reduced to the order of  $O(q\log(q))$ , a large number of multiplications remains necessary to perform the update of the nodes in the graph.

The log-BP algorithm [22] performs the four decoding steps in the logarithmic domain to allow a hardware layout less sensitive to quantization errors, and therefore better suited to fixed-point arithmetic. However, the update of the CNs always requires a

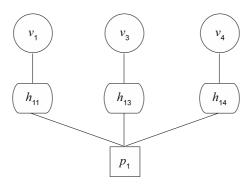

Figure 2.3: The main algorithms for optimal NB-LDPC decoding [7].

large amount of calculation and the complexity of the decoder remains dominated by  $O(q^2)$ . A direct combination of the FFT-BP and log-BP algorithms is not advantageous because the calculation of the Fourier transform is very complex in the logarithmic domain.

To simultaneously benefit from the advantages of the FFT-BP and log-BP algorithms, Song et al. proposed in [20] the log-BP-FFT algorithm. In this algorithm, the VNs are processed in the logarithmic domain. The extrinsic messages of the VNs undergo a double transformation to pass from the logarithmic domain to the probabilities domain and from the probabilities domain towards the frequency domain in which the CNs will be processed. The extrinsic messages of the CNs in turn undergo a double transformation to return back to the logarithmic domain of the VNs. However, the log-BP-FFT algorithm requires look-up tables to ensure the conversion between the probabilities domain and the logarithmic domain. These tables have the disadvantage of consuming a lot of memory resources, a consumption that increases with the degree of parallelism of the decoder. Fig. 2.3 illustrates the steps of the different decoding algorithms mentioned above.

The BP [19], FFT-BP [21], log-BP [22] and log-BP-FFT [20] algorithms are optimal decoding algorithms because they do not use any mathematical approximation to reduce the complexity of the decoding. The BP algorithm and its variants guarantee optimal decoding performance but they are not of great interest for a hardware imple-

mentation. Therefore, other algorithms based on approximations of the BP algorithm are proposed in order to ensure a reasonable performance/complexity tradeoff. We cite mainly the algorithm Min-Sum [22] and its variant EMS (Extended Min-Sum) [24,25]. A detailed comparison of the optimal and suboptimal algorithms cited above can be found in [26]. Besides the EMS algorithm, there is also the Min-Max algorithm [27] which can be considered as an approximation of the Min-Sum algorithm, and which consequently provides poorer performance.

In what follows, we detail the algorithms BP, log-BP, Min-Sum, EMS and Min-Max. We adopt the following mathematical convention: Let  $V = [v_0, v_1, \ldots, v_{n-1}]$  be vector composed of n elements. If i is a positive integer or zero, the notation V(i) indicates the element of position i in V. If  $\beta \in GF(2^m)$ , the notation  $V[\beta]$  indicates the element associated with the symbol  $\beta$  in V.

#### 2.2.1 BP algorithm

Let  $c = [c_0, c_1, \ldots, c_{N-1}], c_i \in GF(q)$ , be the transmitted codeword. The decoding algorithm should converge toward a valid codeword  $\hat{c} = [\hat{c}_0, \hat{c}_1, \ldots, \hat{c}_{N-1}]$  from  $y = [y_0, y_1, \ldots, y_{N-1}]$ , the noisy version of c. The decoding is successful if  $\hat{c} = c$ .

In the BP algorithm, the intrinsic information of the VN  $v_i$  is a q-ary vector of a posteriori probabilities defined as:

$$I_i = [p(v_i = \beta_0 | y_i), p(v_i = \beta_1 | y_i), \dots, p(v_i = \beta_{g-1} | y_i)]$$

(2.6)

where p(a|b) is the conditional probability of a given b.

Let i = 0, 1, ..., M - 1 and j = 0, 1, ..., N - 1. If the element  $h_{ij}$  of the PCM H is not zero then  $M_{v_jp_i}$  denotes the message sent by the VN  $v_j$  to the CN  $p_i$  and  $M_{p_iv_j}$  the message sent by the CN  $p_i$  to the VN  $v_j$ . The steps of the BP algorithm are:

- (a) Initialization: Each VN  $v_i$  transmits its intrinsic information to the CNs connected to it.

- (b) Permutation: Before entering CN  $p_i$ , the message  $M_{v_jp_i}$  is multiplied by the non-zero element  $h_{ij}$  of the PCM. The resultant message  $\tilde{M}_{v_jp_i}$  is computed as:

$$\tilde{M}_{v_i p_i}[\beta] = M_{v_i p_i}[\beta.h_{ij}] \qquad \beta \in GF(q)$$

(2.7)

(c) CN update: the update of the CN  $p_i$  is given by:

$$M_{p_i v_j}[\beta] = \sum_{\substack{s \neq j \\ h_{is} \neq 0}} \prod_{\substack{s \neq j \\ h_{is} \neq 0}} \tilde{M}_{v_s p_i}[\theta_s]$$

(2.8)

where  $\beta$  and  $\theta_s$  are GF(q) symbols. The update of  $p_i$  is done by calculating the probability of all symbol combinations that satisfy the parity equation.

(d) Inverse permutation: Before entering VN  $v_j$ , the message  $M_{p_iv_j}$  is divided by the non-zero element  $h_{ij}$  of the PCM. The resultant  $\tilde{M}_{p_iv_j}$  is obtained as:

$$\tilde{M}_{p_i v_j}[\beta] = M_{p_i v_j}[\beta.h_{ij}^{-1}] \qquad \beta \in GF(q)$$

(2.9)

(e) VNs update: A VN  $v_j$  receives  $d_v$  messages  $\tilde{M}_{p_iv_j}$  and generates  $d_v$  messages  $M_{v_jp_i}$ . Outgoing messages from  $v_j$  are computed by (2.10). Each outgoing message is a function of all incoming messages to  $v_j$  except the one from  $p_i$ .

$$M_{v_j p_i}[\beta] = \mu_{v_j p_i} \times I_j[\beta] \times \prod_{\substack{s \neq i \\ h_{sj} \neq 0}} \tilde{M}_{p_s v_j}(\beta) \qquad \beta \in GF(q)$$

(2.10)

where  $\mu_{v_jp_i}$  is a normalization factor such that  $\sum_{\beta\in\mathrm{GF}(q=2^m)}M_{v_jp_i}[\beta]=1$ .

(f) Estimation of the codeword: at every iteration, the *a priori* probability vector  $(APP_i)$  is computed as follows:

$$APP_{j}[\beta] = \mu_{v_{j}}.I_{j}[\beta]. \prod_{h_{s,j\neq 0}} \tilde{M}_{p_{s}v_{j}}(\beta) \qquad \beta \in GF(q)$$

(2.11)

where  $\mu_{v_j}$  is a normalization factor such that  $\sum_{\beta \in GF(q=2^m)} APP_j[\beta_i] = 1$ . The decision is made based on selecting the symbol of highest probability in  $APP_j$  as:

$$\hat{c}_j = \underset{\beta \in GF(q)}{\operatorname{argmax}} \{ APP_j[\beta] \} \qquad j = 0, 1, \dots, N - 1$$

(2.12)

If the set of symbols of  $\hat{c}_j$  forms a codeword then the decoding is considered as finished.

#### 2.2.2 Log-BP algorithm

The reliability of a symbol can be measured by the Log-Likelihood Ratio (LLR) as defined in the following equation:

$$LLR(\beta) = \ln \frac{p(v_j = \beta | y_j)}{p(v_j = \beta_0 | y_j)} \qquad \beta \text{ and } \beta_0 \in GF(q)$$

(2.13)

On the one hand, replacing the probabilities with LLRs in (2.8, 2.10, and 2.11) transforms the multiplication operations into additions and on the other hand reduces the quantization errors. Thus, in the log-BP algorithm, the intrinsic information of a VN  $v_i$  is defined by:

$$I_{j} = \left[0, \ln \frac{p(v_{j} = \beta_{1}|y_{j})}{p(v_{j} = \beta_{0}|y_{j})}, \dots, \ln \frac{p(v_{j} = \beta_{q-1}|y_{j})}{p(v_{j} = \beta_{0}|y_{j})}\right]$$

(2.14)

The messages circulating on the bipartite graph are composed by LLRs. The log-BP algorithm keeps the same steps of the BP algorithm while modifying the update equations. The update of a VN  $v_i$  is described as:

$$M_{v_j p_i}[\beta] = I_j[\beta] + \sum_{\substack{s \neq i \\ h_{si} \neq 0}} \tilde{M}_{p_s v_j}(\beta) \qquad \beta \in GF(q)$$

(2.15)

The update of CN  $p_i$  is computed as:

$$M_{p_i v_j}[\beta] = \ln\left(\sum_{\substack{s \neq j \\ h_{is} \neq 0}} \exp\left(\sum_{\substack{s \neq j \\ h_{is} \neq 0}} \tilde{M}_{v_s p_i}[\theta_s]\right)\right) \qquad \beta \in GF(q)$$

(2.16)

Finally, the update of the a priori information can be written as:

$$APP_{j}[\beta] = I_{j}[\beta] + \sum_{h_{s,j} \neq 0} \tilde{M}_{p_{s}v_{j}}(\beta) \qquad \beta \in GF(q)$$

(2.17)

#### 2.2.3 Min-Sum algorithm

The Min-Sum algorithm is proposed in [24] to reduce the complexity of the log-BP algorithm by making an approximation of (2.16). Indeed, in the Min-Sum algorithm, the update of CN  $p_i$  can be written as:

$$M_{p_i v_j} \approx \max_{\substack{\substack{s \neq j \\ h_{is} \neq 0}}} \left\{ \sum_{\substack{s \neq j \\ h_{is} \neq 0}} \tilde{M}_{v_s p_i} [\theta_s] \right\}$$

(2.18)

Thus, the Min-Sum algorithm simplifies the decoder by eliminating the lookup tables needed to implement the exponential and logarithmic functions, and by minimizing the number of the arithmetic operations.

#### 2.2.4 EMS algorithm and its variants

The EMS caracteristics can be summarized as:

**Truncation of the exchanged messages**: To further simplify the Min-Sum decoder, the authors in [24] introduced the idea of truncating the messages that circulate on the bipartite graph from q to the  $n_m$  most reliable symbols. However, the value of  $n_m$  must be carefully chosen to avoid performance loss.

Extra memories for the GF symbols: In the log-BP algorithm, the messages are vectors composed of q unsorted reliability values. In addition, it is not necessary

to explicitly indicate the value of the symbol associated with each of the reliabilities since it can be easily deduced by its position in the message. Due to truncation, messages from the EMS algorithm must be sorted and symbol values must be explicitly mentioned. The messages that circulate in the bipartite graph are represented as  $M = [(LLR(\theta_k), \theta_k)]_{0 \le k < n_m - 1}$ , such that  $\theta_k$  is a variable in GF(q) and  $LLR(\theta_{k'}) \ge LLR(\theta_{k''})$  if k' < k''. In the following,  $M^{\bigoplus}$  represents the partial message that contains the set of GF symbols of message M and  $M^+$  represents the vector that contains the set of LLRs of the message M. The most reliable symbol in M is  $M^{\bigoplus}(0)$  and the less reliable one is  $M^{\bigoplus}(n_m - 1)$ .

Compensating candidates: The truncation of messages leads to performance degradation that can be compensated by using a constant reliability value noted  $\gamma$  for symbols not retained during truncation. The value of  $\gamma$  is calculated as follows:

$$\gamma = M^{+}(n_m - 1) + O \tag{2.19}$$

in which O is a scalar that can be determined by simulation to minimize the Bit Error Rate (BER) or theoretically as described in [25].

The steps of EMS algorithm can be summarized as follows:

- (a) Initialization: each VN  $v_i$  sends the most  $n_m$  reliable intrinsic information symbols to its set of connected CNs.

- (b) VNs update: A VN  $v_i$  receives  $d_v$  messages  $\tilde{M}_{p_iv_j}$  and a compensation scalar  $\gamma_i$  associated to each  $\tilde{M}_{p_iv_j}$ . The value of  $\gamma_i$  is determined by (2.19). The sorted message  $M_{v_jp_i}$  contains the  $n_m$  most reliable symbols by combining the intrinsic information with the incoming messages except  $p_i$  itself. The reliability of a symbol  $M_{v_jp_i}^{\bigoplus}(k)_{k=0,1,\ldots,n_m-1}$  is obtained by:

$$M_{v_j p_i}^+(k) = I_j[M_{v_j p_i}^{\bigoplus}(k)] + \sum_{\substack{s \neq i \\ h_{s,i} \neq 0}} W_s(k)$$

(2.20)

such that

$$W_s(k) = \begin{cases} \tilde{M}_{p_s v_j}[M_{v_j p_i}^{\bigoplus}(k)] & \text{if } M_{v_j p_i}^{\bigoplus}(k) \in \tilde{M}_{p_s v_j} \\ \gamma_s & \text{else} \end{cases}$$

(c) Permutation: each symbol of  $M_{v_jp_i}$  will be multiplied by the element  $h_{ij} \neq 0$  of the PCM.

$$\tilde{M}_{v_i p_i}^{\bigoplus}(k) = h_{ij} \cdot M_{v_i p_i}^{\bigoplus}(k) \qquad k = 0, 1, \dots, n_m - 1$$

(2.21)

(d) CNs update: the reliability of a symbol of an outgoing message is calculated as in 2.18.  $M_{p_iv_j}$  outgoing messages contain the most reliable  $n_m$  symbols.

(e) Inverse permutation: each symbol of  $M_{p_iv_j}$  will be divided by the element  $h_{ij} \neq 0$  of PCM.

$$\tilde{M}_{p_i v_j}^{\bigoplus}(k) = h_{ij}^{-1} \cdot M_{p_i v_j}^{\bigoplus}(k) \qquad k = 0, 1, \dots, n_m - 1$$

(2.22)

(f) Estimation of the codeword: at every iteration, each VN  $v_j$  updates a vector of  $prior \ LLRs \ APP_j$  as:

$$APP_j[\beta] = I_j[\beta] + \sum_{h_{s,j} \neq 0} W_s(\beta) \qquad \beta \in GF(q)$$

(2.23)

such that

$$W_s[\beta] = \begin{cases} \tilde{M}_{p_s v_j}^+[\beta], & \text{if } \beta \in \tilde{M}_{p_s v_j}^{\bigoplus} \\ \gamma_s, & \text{else} \end{cases}$$

Finally the decision is taken based on (2.12).

# 2.2.5 Min-Max algorithm

The LLR value as defined in sections 1.3.1 and 1.3.3 may assume negative values. However, it would be easier to deal only with positive values. Therefore, the author of [27] proposed the following definition of the LLRs:

$$LLR(\beta) = -\ln \frac{p(x = \beta|y)}{\max_{\theta \in GF(2^m)} \{p(x = \theta|y)\}} \qquad \beta \in GF(2^m)$$

(2.24)

where  $y = (y_0, y_1, \dots, y_{m-1})$  is the channel observation and  $x = (x_0, x_1, \dots, x_{m-1})$  is the transmitted symbol.

In this definition, the normalization is done by the probability of the most reliable symbol. It follows that the LLR of this symbol is always zero and the LLRs of the other symbols are positive.

Also in [27], the author proposed the Min-Max algorithm which allows to simplify the processing at the check nodes level by replacing the sum in (2.18) by the operator max:

$$M_{p_i v_j}[\beta] \approx \min_{\substack{\substack{s \neq j \\ h_{is} \neq 0}}} \{ \max_{\substack{s \neq j \\ h_{is} \neq 0}} \tilde{M}_{v_s p_i}[\theta_s] \}$$

(2.25)

The messages of the Min-Max algorithm can be truncated like in the EMS algorithm.

# 2.3 FB and SB CNs algorithms

This section reviews the two state-of-the-art implementations of the EMS algorithm: the Forward-Backward (FB) [22] and the Syndrome-Based (SB) [23]. Then, the new innovative technique called presorting is introduced to show that sorting the CN input messages can lead to significant savings in terms of computational complexity and hardware implementation.

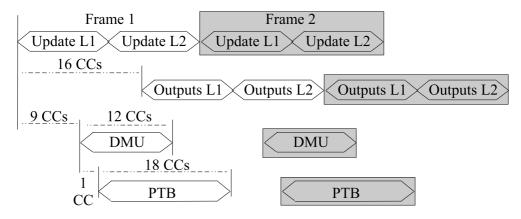

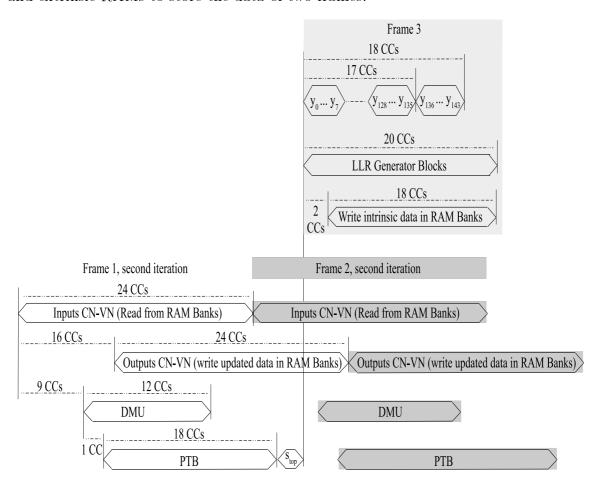

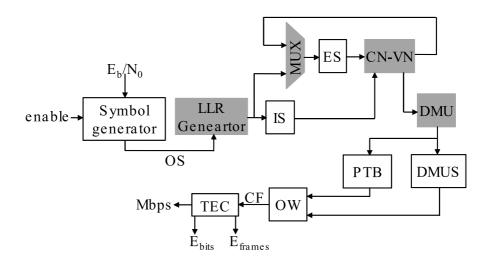

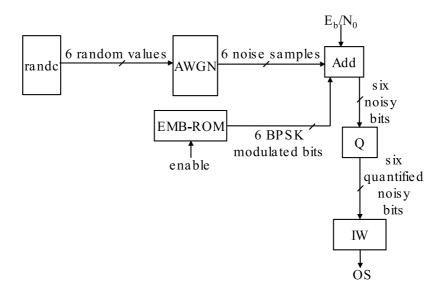

# 2.3.1 Forward-Backward CN processing